# 3-D Hyperintegration and Packaging Technologies for Micro-Nano Systems

These technologies stack and interconnect materials and components to achieve high density, small size, low weight, reduced power, and very low cost.

By JIAN-QIANG LU, Senior Member IEEE

ABSTRACT | Three-dimensional (3-D) hyperintegration is an emerging technology, which vertically stacks and interconnects multiple materials, technologies, and functional components to form highly integrated micro-nano systems. This 3-D hyperintegration is expected to lead to an industry paradigm shift due to its tremendous benefits. Worldwide academic and industrial research activities currently focus on technology innovations, simulation and design, and product prototypes. Anticipated applications start with memory, handheld devices, and high-performance computers and extend to highdensity multifunctional heterogeneous integration of InfoTech-NanoTech-BioTech systems. This paper overviews the 3-D hyperintegration and packaging technologies, including motivations, key technology platforms, status, and perspectives towards commercialization. The challenges associated with the 3-D technologies are addressed, including integration architectures and design tools, yield and cost, thermal and mechanical constraints, and manufacturing infrastructure.

**KEYWORDS** | Hyperintegration; InfoTech-NanoTech-BioTech systems; three-dimensional (3-D) integration; through silicon via; wafer alignment; wafer bonding; 3-D packaging

# I. INTRODUCTION

Three-dimensional (3-D) hyperintegration is an emerging technology that can form highly integrated systems by vertically stacking and connecting various materials, tech-

Manuscript received October 30, 2007; revised March 9, 2008.

Current version published February 27, 2009.

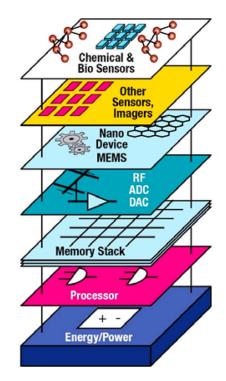

Fig. 1. A vision of future 3-D hyperintegration of InfoTech, NanoTech, and BioTech systems—a new paradigm for future technologies.

nologies, and functional components together, as shown in Fig. 1 [1]. The potential benefits of 3-D integration can vary depending on approach; they include multifunctionality, increased performance, increased data bandwidth, reduced power, small form factor, reduced packaging, increased yield and reliability, flexible heterogeneous integration, and reduced overall costs. For example, a small form factor is achieved by stacking active component layers on top of one another in any 3-D approach. Since simple complementary

This work was supported in part by the Defense Advanced Research Projects Agency, MARCO, and NYSTAR through the Interconnect Focus Center, IBM, Freescale, SEMATECH, and SRC.

The author is with Department of Electrical, Computer, and Systems Engineering and Center for Integrated Electronics, Rensselaer Polytechnic Institute, Troy, NY 12180 USA (e-mail: luj@rpi.edu).

Digital Object Identifier: 10.1109/JPROC.2008.2007458

metal–oxide–semiconductor (CMOS) device scaling has stalled, this third dimension allows extending Moore's law to ever higher density, higher functionality, higher performance, and more diversified materials and devices to be integrated with lower cost. Speaking at the 2006 IEEE International Electron Devices Meeting (IEDM), Dr. C.-G. Hwang, president and CEO of Samsung Electronics, stated that "rapid adoption of 3-D integration technology seems to be essential and, thankfully, unavoidable." [2] It is expected that the industry paradigm will shift to a new industry-fusing technology era that will offer tremendous global opportunities for expanded use of 3-D silicon-based technologies in highly integrated systems. Indeed, 3-D integration is recognized as an enabling technology for future ICs and lowcost micro/nano/electroopto/bio heterogeneous systems.

This paper attempts to provide an overview of the 3-D hyperintegration and packaging technologies, to discuss their benefits and applications, and to address key challenges associated with the 3-D technologies. The author believes that many unique system architectures will be realized with 3-D integration and hopes that this paper motivates IC system architect designers to extend their horizons to 3-D hyperintegration.

# **II. 3-D INTEGRATION APPROACHES**

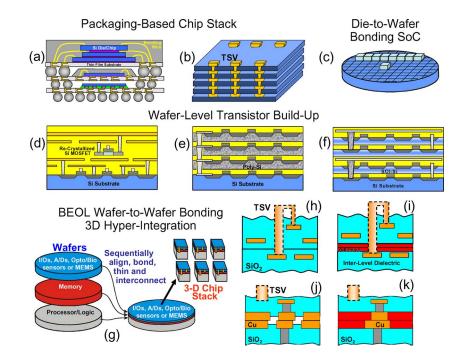

Various 3-D technologies are currently pursued, as illustrated in Fig. 2. They can be divided into three categories based on their similarity to other technologies:

1) 3-D packaging technology [Fig. 2(a)–(c)];

- 2) transistor build-up 3-D technology [Fig. 2(d)–(f)];

- monolithic, wafer-level, back end of the line (BEOL)-compatible 3-D technology [Fig. 2(g)-(k)].

Each 3-D technology is briefly described below, with possible application examples showing the worldwide research and development activities.

# A. Packaging-Based 3-D Integration

Packaging-based 3-D integration, i.e., the stacked chipscale package (CSP) as called historically, is enabled by wire bonding and flip-chip bonding as depicted in Fig. 2(a). These include system-in-package (SiP), which is formed by stacking thinned chips with wire bonding to connect them, and package-on-package (PoP), which is formed by stacking packages such as SiPs with flip-chip bonding. These SiPs or PoPs are already commercially available products, particularly widely used in cell phones [3], [4], [91]. Today's new cell phones have at least one SiP or PoP, while more than a billion cell phones were delivered in 2006.

# B. Die-to-Die 3-D Integration

Die-to-die 3-D integration is enabled by thinned die-todie bonding and through silicon via (TSV) interconnections, as depicted in Fig. 2(b). The TSVs are typically formed by laser drilling, such as a prototype eight-die memory stack by Samsung [5] or deep reactive ion etching (DRIE), such as a Bosch process [6], [7], followed by liner deposition and copper fill.

Fig. 2. Schematic representations of major 3-D integration approaches: (a)-(c) 3-D packaging technology, (d)-(f) wafer-level transistor buildup 3-D technology, and (g)-(k) wafer-level BEOL-compatible 3-D technology.

#### C. Die-to-Wafer 3-D Integration

Die-to-wafer 3-D integration as depicted in Fig. 2(c) is enabled by die-to-wafer bonding, with interchip electrical interconnections formed by postbond via formation [8] or solder (or eutectic) bonding during the die bonding process [9]. This approach uses techniques from both packaging and wafer fabrication, such as die pick-and-place and TSV formation, respectively. A system-on-chip (SoC), which is difficult to be fabricated with two-dimensional (2-D) integration, may be realized with several smaller chips stacking on a large chip [8].

#### D. Transistors Formed Inside On-Chip Interconnect

The approach to form transistors inside on-chip interconnect layers on a piece of recrystallized silicon film is depicted in Fig. 2(d). A small piece of amorphous silicon film is deposited with a catalyst followed by either laser heating or rapid thermal anneal to recrystallize the silicon [10], [92]. The transistors are then formed by BEOL compatible processing. These transistors may be used to form repeaters for on-chip interconnects or signal amplifiers for optical interconnects.

#### E. Transistors Formed on Polysilicon Films

The approach to form transistors on polysilicon films layer by layer with tungsten interlayer vias is depicted in Fig. 2(e). After the first layer of transistors is completed, an amorphous silicon film is deposited and converted to polysilicon by laser heating or rapid thermal anneal [11]. The tungsten via can tolerate the relatively high temperatures ( $\sim 600$  °C) needed for polysilicon conversion and transistor formation. These transistors may be used to fabricate low-performance nonvolatile memory [11].

#### F. Transistors Formed on Single-Crystal Silicon Films

The approach to form transistors on single-crystal silicon films layer by layer is depicted in Fig. 2(f). The silicon layer can be bonded onto the oxide surface of a previously fabricated transistor layer by transferring the crystal silicon film from a silicon-on-insulator (SoI) wafer. The interstrata via is filled with polysilicon and/or tungsten, enabling device fabrication at relatively high temperature. Very high-density SRAMs and NANDs are demonstrated with this approach [2], [12], [13].

# G. Wafer-Level BEOL-Compatible 3-D Hyperintegration

Monolithic wafer-level BEOL-compatible 3-D hyperintegration is enabled by wafer alignment, bonding, thinning, and interwafer interconnections, as depicted in Fig. 2(g)-(k). All approaches shown use TSVs to form the interwafer interconnects (i.e., interstrata interconnects, interwafer vias, or interstrata vias). They differ as to when the via is formed, before/during bonding (via first) or after bonding (via last). In addition, a variety of bond layer types can be chosen. Four major bonding and interstrata interconnection approaches are highlighted in Fig. 2(h)-(k):

- via last, oxide-to-oxide bonding [Fig. 2(h)];

- via last, adhesive (polymer) bonding [Fig. 2(i)];

- via first, copper-to-copper bonding [Fig. 2(j)];

- via first, bonding of damascene-patterned metal/ adhesive redistribution layer [Fig. 2(k)].

Academic and industrial organizations are actively developing a variety of wafer-level 3-D technologies [14]–[39]. Many organizations are currently evaluating competing wafer-level 3-D technologies [2], [14], [23], [24], [26], [31], [36], [37].

There are also other approaches not shown in Fig. 2, such as forming the TSVs during the front end of the line (FEOL) processing [29], stacking chips with metallization on the stack lateral side [40], stacking chips on silicon carrier with TSVs [41], or combining various approaches.

Wafer-level BEOL-compatible 3-D hyperintegration is perhaps the most promising 3-D integration for highvolume production of highly integrated micro-nano systems. More details of these wafer-level 3-D platforms and their key enabling unit processes are discussed in the next section.

# III. WAFER-LEVEL BEOL-COMPATIBLE 3-D HYPERINTEGRATION

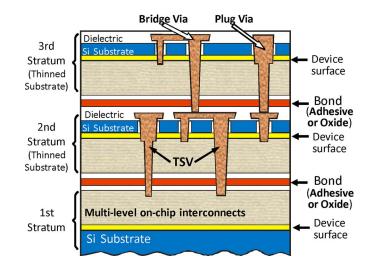

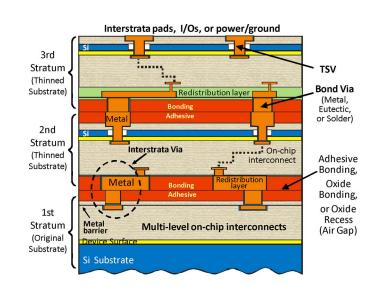

Wafer-level BEOL-compatible 3-D hyperintegration can be categorized into two platforms, i.e., via-last and via-first 3-D platforms, as illustrated in Figs. 3 and 4, respectively.

For the via-last 3-D platform as shown in Fig. 3, the interstrata vias are formed after the wafers are aligned and bonded, and the top wafer backside is thinned. Since these vias are usually formed through a silicon layer, they are also called through silicon vias. The TSV usually consists of an electrical isolation layer (e.g.,  $SiO_2$  or other dielectrics), liner or barrier layer (e.g., titanium, tantalum, TiN, or TaN), and a via metal (e.g., copper, tungsten, or highly doped polysilicon). The wafers can be attached by either adhesive-to-adhesive bonding [15], [18] or oxide-to-oxide bonding [24], [26].

For the via-first 3-D platform as shown in Fig. 4, the majority of interstrata vias can be formed during the wafer bonding process (right after wafer alignment) but before the top wafer backside is thinned. To differentiate TSVs, thus bonded interstrata vias can be called "bond vias." For some cases, wafers are bonded only by these bond vias. Similar to the TSV, the bond via also consists of an electrical isolation layer, a liner or barrier layer, and a via metal, while the candidates for the via metal can be elemental metals (e.g., copper, gold), eutectic conductors, or solders (e.g., InAu, CuSn). Besides the metal bonding that forms the interstrata interconnects (bond vias), the bonding interface can include adhesive-to-adhesive bonding (such a platform is called a metal/adhesive via-first 3-D platform [16], [17]), oxide-to-oxide bonding (such a

Fig. 3. Schematic cross-section of three-stratum stack of via-last 3-D platform, showing bonding interface and vertical interstrata vias (TSVs). The bonding interface can be either adhesive-to-adhesive bonding [15], [18] or oxide-to-oxide bonding [24], [26].

platform is called a direct bonded interconnect [42]), or leaving an air gap by recessing the dielectrics surrounding the metal bonding posts [23], [29].

For wafer-level BEOL-compatible 3-D platforms, only four key enabling unit processes are required, as discussed below.

1) Wafer-to-Wafer Alignment: A wafer-level alignment accuracy of one micrometer or smaller has been achieved, which is sufficient for most applications. Wafer alignment tools were developed for microelectromechanical systems (MEMS). New wafer alignment tools have been further developed for wafer-level 3-D integration [21], including infrared (IR) aligner (limited to IR transparent wafers) [26] and SmartView aligner for aligning wafers face-to-face or face-to-back [22], [43]–[45]. Mechanical interlock structures have also been demonstrated for fine alignment [46].

2) Wafer-to-Wafer Bonding: A bonding temperature compatible with BEOL processing (e.g.,  $\leq 400$  °C) and a bonding interface thickness of one micrometer or smaller have been achieved. Wafer bonding was also developed initially for MEMS. It has been greatly researched for BEOL-compatibility and wafer-scale void-free bonding, which limit the wafer bonding to low temperature and use of nonoutgassing materials as the bonding intermediate

Fig. 4. Schematic cross-section of three-stratum stack of via-first 3-D platform, showing bonding interface and vertical interstrata vias (bond vias and TSVs). Besides the metal bonding that forms the interstrata interconnects, the bonding interface can include an adhesive-to-adhesive bonding [16], [17] or oxide-to-oxide bonding [42], or leave an air gap by recessing the dielectrics surrounding the metal bonding posts [23], [29].

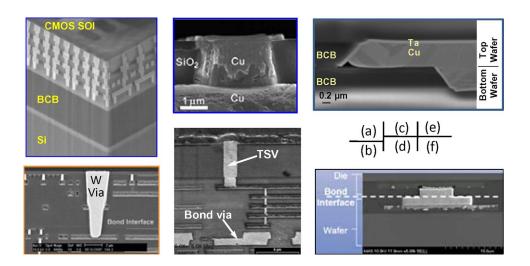

**Fig. 5.** Representative bonding interfaces with images adapted from the literature: (a) adhesive (BCB) bonding of an Sol CMOS wafer on an Si wafer with the electrical characteristics of CMOS devices and circuits unaffected [15], [19]; (b) PECVD oxide bonding with tungsten (W) via shown for advanced focal planes [26]; (c) Cu interconnect bonded to Cu pad showing a high-quality bonding interface [23]; (d) Cu bonding for bond vias with "supercontact" TSV shown [29]; (e) bonding of damascene patterned Cu/BCB redistribution layers for metal/adhesive via-first 3-D platform [16]; and (f) bonding of metal/oxide layers using direct oxide bond for a direct bonded interconnect (DBI) 3-D approach (the information about the metal material was not released) [42].

materials, such as nonoutgassing adhesives [21], [25], [32], [43], [45], [47]–[49], plasma-enhanced chemical vapor deposition (PECVD) oxide [24], [26], and few metals (e.g., copper [23], [27]–[31], titanium [50], [51], InAu [33], and CuSn [52]). Fig. 5 shows cross-sectional images of representative wafer bonding interfaces. Table 1 lists four key wafer bonding approaches demonstrated so far and key parameters differentiating their advantages and challenges for high-volume manufacturing.

3) Wafer Thinning: A range of submicrometer to 100  $\mu$ m with adequate uniformity has been achieved. One wafer thinning approach is to use an etch-stop, i.e., the top wafer backside is thinned by backside grinding, optional chemical-mechanical polishing (CMP), and selective wetetching to an etch stop, e.g., an ion implanted layer, a

graded SiGe epitaxial layer, or a buried oxide (BOX) layer with SoI wafers. An excellent control of the thinning uniformity and thickness (down to a few tens of nanometers) can be achieved [15], [18]-[20], [26]. Another approach is a thickness-control removal of silicon, which is used for bulk wafers without an etch-stop. It is therefore expected that the thinned wafer is relatively thick (e.g., in a range of a few tens or hundreds of micrometers) with limited thickness uniformity (in a range of a few to few tens of micrometers) [36], [43], [45], [53]. Other approaches are also demonstrated with TSVs as a thinning stopper, where the TSVs are formed either during the FEOL process [29] or after the BEOL process but right before wafer alignment and bonding [36], [53]. If the wafers are bonded back-to-face (i.e., back of the top wafer is bonded onto the face of the bottom wafer or wafer

| Table 1 Key Bonding Approache | for Wafer-Level 3 | 3-D Technologies* |

|-------------------------------|-------------------|-------------------|

|-------------------------------|-------------------|-------------------|

| Bonding<br>Approach<br>Key Parameters                                                                                              | Oxide<br>Via-Last | Adhesive<br>Via-Last | Copper<br>Via-First | Copper/<br>Adhesive |  |  |

|------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------|---------------------|---------------------|--|--|

| Bonding Temperature                                                                                                                | Fair              | Low                  | High                | High                |  |  |

| Surface Planarity                                                                                                                  | Strict            | Loose                | Strict              | Strict              |  |  |

| Bond Strength                                                                                                                      | Good              | High                 | Good                | Good                |  |  |

| Bond Integrity                                                                                                                     | Fair              | High                 | Good                | High                |  |  |

| Via Density                                                                                                                        | Low               | Low                  | High                | High                |  |  |

| Thermal Management                                                                                                                 | Fair              | Fair                 | Good                | Best                |  |  |

| Complexity                                                                                                                         | High              | Fair                 | Fair                | High                |  |  |

| *Color codes: green (light dark) for most desirable to manufacturing;<br>yellow (light) for adequate; and red (dark) for concerns. |                   |                      |                     |                     |  |  |

Authorized licensed use limited to: University of Illinois. Downloaded on October 12, 2009 at 12:05 from IEEE Xplore. Restrictions apply.

stack), a handling wafer (or temporary carrier wafer) is needed to provide the mechanical support during thinning and handling of the thinned wafer [36], [53].

4) Interwafer Interconnection: A via diameter in a range of a few micrometers with high via height-to-diameter aspect ratio has been achieved. Both TSVs and bond vias can be formed by via etching and clean, liner deposition, metal fill, and CMP-similar to a BEOL damascene patterning process developed for on-chip copper interconnects. Actually, the bond vias have been formed using the BEOL damascene patterning process as shown in Fig. 5(c) to (e) [16], [23], [29]. The TSVs have been formed 1) before or during the FEOL process using polysilicon [33] or tungsten [29] as the via filling material; 2) after the FEOL or BEOL process using copper as the via filling material with/without a carrier wafer for wafer thinning [29], [36], [53]; or 3) after wafer bonding and thinning [15], [26], as shown in Fig. 5(b). Since the TSVs usually pass through the thinned silicon wafer and/or onchip interconnects, their diameter and height-to-diameter aspect ratio are usually much larger than the bond vias. Hence the TSV density is relatively lower than that of bond vias because of the limitations associated with the current TSV processing technologies, TSV resistance, and silicon real estate consumption of the TSVs.

Feasibility for all these four key processes has been demonstrated. No technology show-stoppers are expected. Technology variations are being investigated for prototyping and commercialization, including:

- face-to-face or face-to-back alignment and bonding;

- with or without handling wafers (carrier wafers);

- with or without etch-stop for wafer thinning;

- when and how to form the interstrata vias.

Based on the 3-D technology developments so far, it is clear that the key advantage of the via-last 3-D approach is that the wafer bonding process is separated from interstrata via formation. Therefore, a robust mechanical/ chemical wafer bond, for instance, using benzocyclobutene (BCB) as shown in Fig. 5(a) [15], [18]-[20], can be easily achieved compared to the via-first 3-D approach. The key concern for the via-last 3-D approach is that the TSV density could be low because of the large via diameter required for long TSVs to pass through the thinned silicon substrate, particularly if a bulk silicon wafer is used. If an SoI wafer is used for the top wafer, a high density of short TSVs can also be achieved using BEOL damascene patterning process through the BOX/SoI layer because the bulk silicon substrate of the SOI wafer can be completely removed, leaving only the BOX/SoI layer with a thickness of a few ten to a few hundred nanometers [19], [20], [26]. In fact, these TSVs are formed through the SiO<sub>2</sub> layer surrounding the SoI CMOS device islands; there is no silicon layer for TSVs to go through. Therefore, the term "TSVs" could be used more generically for "through strata vias."

The key advantages of the via-first 3-D approach are that 1) a high density of bond vias can be formed at the bonding interface and 2) the formation of bond vias and wafer bonding are done in one unit process. Particularly, as shown in Fig. 4, the metal/adhesive via-first 3-D platform offers combined process integration advantages of metal-to-metal electrical bonding (e.g., Cu-to-Cu) with the increased adhesion strength and robustness of dielectric adhesive bonding (e.g., using partially cured BCB) [16], [17], [54]. A redistribution layer formed by damascenepatterned metal/adhesive structure provides additional interstrata signal/power routing as well as alleviation of the wafer alignment tolerance [54]. Planarity requirements are stringent but appear to be reasonable [17]. However, if the top wafers are bulk silicon wafers, the density of TSVs, which interconnect the bonded wafers (i.e., the top strata) and bring the I/Os out of the stack, is as limited as that with the via-last 3-D platform. Similar to the via-last 3-D platform, SoI wafer is a better choice as the top wafer in the 3-D stack because its bulk silicon substrate can be removed with BOX as the etch stop; short TSVs can be formed using BEOL damascene patterning process as for bond vias.

Though the use of SoI wafers obviously makes the wafer thinning and TSV formation much easier, and hence low cost, the choice to use SoI or bulk silicon wafer depends on overall processing protocols, components [Si CMOS logic, SRAM, DRAM, NAND, SiGe, radio frequency (RF), etc.] in the system, and the IC manufacturer's preferences. Further research and development is necessary to fully evaluate these promising platforms.

# IV. TECHNOLOGY COMPARISON AND APPLICATIONS

With the significant research progress in 3-D technologies thus far, it is still too early to do a full comparison among various 3-D technologies. We attempt to briefly discuss the key advantages and limitations of different 3-D technologies and their potential applications, as summarized in Table 2. In general, all 3-D technologies would offer *high density* component integration with:

- small form factor (small size and light weight);

- reduced packaging;

- reduced power (fewer I/Os to be driven).

For 3-D packaging technologies [Fig. 2(a)–(c)], using known good die (KGD) can provide a yield advantage. Timeto-market for a new product is short because the flexibility in the assembly process requires less design effort for a new system. However, the cost for high-volume production can be very high because of the testing required for KGDs and the low throughput of pick-and-place assembly. The SiP and PoP approaches [Fig. 2(a)] are already used in portable devices (e.g., cell phones) [3], [4]. The die-stack approach with TSVs [Fig. 2(b)] has been demonstrated for memory stacks [5]. The die-wafer approach [Fig. 2(c)] has the potential for building 3-D SoCs [8].

| Tab | le 2 | 2 3-D | Technologies | and | Potential | Applications |

|-----|------|-------|--------------|-----|-----------|--------------|

|-----|------|-------|--------------|-----|-----------|--------------|

| Technology                                      | Key Advantages<br>Key Concerns                                                                                                                 | Key Applications                                                                                                                                                                                        |  |  |

|-------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3D Packaging                                    | KGDs; Heterogeneous<br>integration<br>Low throughput for high<br>volume production                                                             | Memory stack; memory stack to<br>microprocessor; discrete device<br>integrated with ICs                                                                                                                 |  |  |

| Transistor<br>Build-Up 3D<br>Technology         | Wafer-level lithography and<br>processing<br>Thermal and material<br>constraints                                                               | Highest density memory;<br>low performance CMOSs                                                                                                                                                        |  |  |

| Wafer-Level<br>BEOL-Compatible<br>3D Technology | Massive, short interstrata via;<br>Heterogeneous integration;<br>Low cost for high volume<br>production<br>Design and technology<br>complexity | Any highly integrated systems<br>requiring high performance, high<br>data bandwidth and low power,<br>e.g., memory, memory-intensive<br>processors, imagers, mixed signal<br>and wireless communication |  |  |

Transistor buildup 3-D technology [Fig. 2(d)-(f)] can achieve the highest density of silicon transistors with wafer-level fabrication using advanced photolithography. Wafer-level processing can also reduce costs for highvolume production. However, the processing constraints (particularly the thermal budget) affect the properties of the transistors and limit the material choices mostly to silicon and tungsten. The silicon recrystallization approach [Fig. 2(d)] could be used for fabrication of repeaters within on-chip interconnect to alleviate interconnect delay [10], [92]. The poly-Si layer approach [Fig. 2(e)] is used for lowperformance memory [11]. The bonded crystalline silicon approach [Fig. 2(f)] can be used for a NAND flash memory stack [2], [13]. Companies, such as Samsung, that manufacture cell phones and handhelds see great potential for a high-density memory stack [2].

For wafer-level BEOL-compatible 3-D technology [Fig. 2(g)-(k)], the electrical, RF, optical, thermal, and mechanical behavior can be considered for each component separately. For example, the starting yield can be improved by fabricating logic and memory on separate wafers with optimized materials and process technologies. The separate wafers are then stacked using a monolithic wafer-level BEOL-compatible process for all components, potentially improving the cost and overall system yield at high-volume production. Typically the bottom wafer retains its full thickness and serves as a mechanical support for the stack. Each subsequent wafer is then thinned to micrometer scale after stacking (bonding); thus the overall stack thickness is close to that of a single wafer and can be processed and packaged with current wafer technologies. Massive (millions), short (micrometer-scale) interstrata interconnects (vias) provide extremely high data bandwidth and dramatically decrease interconnect delay and power consumption.

Wafer-level BEOL-compatible 3-D hyperintegration is perhaps the most attractive 3-D technology due to its flexibility for monolithic heterogeneous integration of different materials, processing technologies, and functional components with additional benefits in cost and performance. Many research groups are exploring its potential applications, such as improving interconnect delay [55]–[60], [93], memory stacks [29], [59], [61], memory-processor or logic–logic stacks [29], [62]–[65], signal-processing circuits [66], [67], field-programmable gate arrays (FPGAs) [68], [69], imagers [26], [70], mixedsignal and RF [70]–[72], and 3-D power delivery [73], [74]. Design and simulation tools have been demonstrated, such as for electronic computer-aided design (ECAD) tools [55]–[69], [93], [75]–[80], switching energy, and thermal and mechanical simulations [59], [60], [65], [79]–[81].

# V. KEY CHALLENGES ASSOCIATED WITH 3-D INTEGRATION

Present FEOL device technologies, such as strained layers, high-k gate dielectrics, metallic gates, and wrap-around gate structures, are resulting in enhanced digital CMOS devices at the 45 and 32 nm technology nodes. By the 22 nm node, these FEOL enhancements will result in another interconnect bottleneck with Cu damascene patterning and low-k interlevel dielectrics. Wafer-level 3-D is perhaps the only viable near-term alternative to planar ICs with Cu/lowest-k interconnects, as well as enabling heterogeneous integration of different planar technologies for innovative SoCs. The technology and infrastructure challenges that must be overcome before or soon after a decision to move to large-volume manufacturing are discussed in this section, which are split into technological challenges, yield, test and cost challenges, thermal and power challenges, and infrastructure challenges.

### A. Technological Challenges

The three major 3-D technologies (i.e., chip-stack, transistor buildup, and wafer-level stack) will perhaps coexist for a long time, while the chip-stack technology is relatively mature (though its limitation is also clear). Technological challenges include development of cost-effective manufacturable 3-D processes and evaluation/selection of various 3-D platforms for a given application or system. Recent processing developments focus on TSVs because they can be used for both wafer-level 3-D integration and packaging-based 3-D integration [38]. Table 3 lists the need for all the processing technologies and the need for equipment, which is discussed in the infrastructure section.

For wafer-level 3-D integration, there are a number of technological choices, as discussed in Section III. The feasibility of the wafer-level 3-D unit processes, i.e., alignment, bonding, thinning, and interstrata interconnection, have been demonstrated, as summarized below [22]–[39], [42]–[54]:

- wafer-to-wafer alignment accuracy: ~1 μm;

- wafer bonding interfaces: adhesive (e.g., BCB), oxide, metal (e.g., Cu), and combinations (Cu/BCB);

- wafer bonding thickness: ~1 μm at T ≤ 400 °C;

- wafer thinning (remaining silicon thickness):  $\sim 0.1~\mu{\rm m}$  for SoI wafer,  ${\sim}15~\mu{\rm m}$  for bulk Si wafer;

- interstrata interconnects (vias): 2–10  $\mu$ m in diameter.

Wafer bonding determines the 3-D integration integrity, while the alignment accuracy, wafer thinning, and interstrata interconnect formation determine the interstrata interconnect length and density, and hence the interconnect delay reduction (system performance) and data bandwidth. All these unit processes require further research and development before 3-D technology is mature enough for high-volume manufacturing.

### B. Yield, Test, and Cost Challenges

Yield is related to test; yield, test, and throughput drive the cost. 3-D yield and test are certainly a concern; that is why 3-D packaging by wire-bonding KGDs first found its applications in the handheld devices (e.g., memory stacks for cell phones). However, planar (2-D) memories already use redundancies and error-correcting codes (ECCs) to minimize the effects of yield loss [82], [83]; the question of KGD has already been answered for existing memory chips. Moreover, redundant processor cores are also implemented to increase 2-D system yield; for instance, the Sony Playstation 3 requires only seven of eight cores to work in its IBM CELL multiprocessor [84], [85]. Furthermore, current 2-D SoCs, such as Intel's dual-core multithreaded Xeon processor [82], use not only redundancies and ECC for memory but also design-for-testability (DFT), built-in self-test (BIST), and scan and observability registers to accelerate the yield learning processes and to produce KGDs from imperfect chips. Three-dimensional integration will benefit from redundancy, ECC, DFT, BIST, and defect/fault tolerant designs in overcoming the challenges in its yield, test, and cost while providing a more flexible platform for novel implementation of the yield enhancements; for instance, a stratum of phasechange nonvolatile memory (PCNVM, or PCM) could be used to effectively repair faulty chips.

While die yield and test issues need to be considered further, smaller die and wafer-specific processing indicate that yield may not be a limiting factor with a robust monolithic wafer-level 3-D process. Actually, 3-D integration inherently improves the yield since heterogeneous structures (analog circuits, processors, and various types of memory) can be fabricated on separate wafers with differing fabrication procedures and materials optimized for that technology. This would be impossible in 2-D for the same system. Moreover, monolithic wafer-level approaches have many performance advantages, such as a very high density of low parasitic interstrata interconnects

| Tabl | e 3 | Key | 3-D | Technologies | and | Equipment | Needs* |

|------|-----|-----|-----|--------------|-----|-----------|--------|

|------|-----|-----|-----|--------------|-----|-----------|--------|

| Alignment a                                                                                                                                                                                                                                                                                                                                                    | and Bonding   | Via Etching                  | Via Filling                     | Wafer Thinning                                                 |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|------------------------------|---------------------------------|----------------------------------------------------------------|--|--|

|                                                                                                                                                                                                                                                                                                                                                                |               |                              |                                 |                                                                |  |  |

| C2C                                                                                                                                                                                                                                                                                                                                                            | W2W           |                              |                                 |                                                                |  |  |

|                                                                                                                                                                                                                                                                                                                                                                | Un            | it Processing Tech           | nologies                        |                                                                |  |  |

| Adhesive, oxide<br>or metal<br>bondingAdhesive, oxide<br>or metal<br>bondingChip alignmentWafer alignment                                                                                                                                                                                                                                                      |               | Laser drilling<br>or<br>DRIE | ECD<br>or<br>CVD,<br>and<br>PVD | Mechanical grinding,<br>CMP,<br>Wet etching,<br>Plasma etching |  |  |

|                                                                                                                                                                                                                                                                                                                                                                |               | Equipment Nee                | eds                             |                                                                |  |  |

| Chip aligner and                                                                                                                                                                                                                                                                                                                                               | Wafer aligner | Laser drill or<br>DRIE       | Metal<br>deposition, CMP        | Precise thinning                                               |  |  |

| bonder                                                                                                                                                                                                                                                                                                                                                         | Wafer bonder  | Photolitho                   | Photolitho                      | Temporary bonding                                              |  |  |

| * <i>Abbreviations:</i> C2C for chip-to-chip (or die-to-wafer) stack; W2W for wafer-to-wafer stack; DRIE for deep reactive ion etching; ECD for electrochemical deposition (electroplating); CVD for chemical vapor deposition; PVD for physical vapor deposition; CMP for chemical-mechanical planarization (polishing); and Photolitho for photolithography. |               |                              |                                 |                                                                |  |  |

for high bandwidth and increased noise immunity. Most important, lower cost for high-volume interconnects should be possible with monolithic wafer-level processes, compared to 3-D KGD packaging. The chip-on-wafer approach can be used to salvage particularly bad wafers.

In particular, effective 3-D implementation would benefit from the development of a mature BIST waferprobe technology because 1) it provides at-speed testing, with a minimum number of probes per chip; 2) it allows all chips on a wafer to be tested simultaneously; and 3) it provides the thorough testing needed for rapid yield learning and/or imperfect chip repair. While wafer-level test and repair for each stratum are important similar to processing monitors in 2-D implementations, critical test and repair will be conducted after 3-D wafer processing, dicing, and packaging just as the critical test and repair in 2-D implementations are conducted after chip packaging.

## C. Thermal and Power Challenges

Thermal issues arise from increasing electrical power density with the continuous scaling of the ICs, i.e., feature size shrinking of transistors and interconnects and performance and functionality increases of systems. Feature size shrinking leads to increased transistor leakage power loss and interconnect joule power loss; increasing performance and functionality leads to increased dynamic power loss in logic transistors, interconnects, and repeaters for the interconnects. These power losses in turn increase the temperature in the IC chip. The power for today's microprocessor is around 100 W, with a power density in a range of 100 to 300 W/cm<sup>2</sup> or higher at hot spots. Thermal and power issues are of huge concern for 2-D ICs [85], which is the reason that various FEOL technologies (e.g., high-k gate dielectrics and novel CMOS structures), BEOL technologies (e.g., Cu/low-k processes), circuit designs (e.g., multicore multithreaded processors), and various thermal management technologies are being aggressively pursued to alleviate power and thermal constraints.

Thermal and power constraints are of great concern with any 3-D microarchitecture because die stacking could dramatically increase power density if two highly active regions were stacked on top of each other; such a case should be avoided. Heat dissipation is also challenged by the fact that each additional die is stacked farther and farther from the heat sink. This physical distance results in higher thermal resistances and potentially creates thermal isolation leading to self-heating of additional die.

However, 3-D implementation does not necessarily produce extraordinary increases in chip temperatures, and the power consumption and chip temperature can be even reduced if circuits are properly partitioned and arranged horizontally across each die and vertically across different circuit strata. Thermal-aware 3-D floor-planning is the key [64], [65], [76], [79], [80]. In fact, studies, based on detailed analysis and simulation of state-of-the-art micro-

processors implemented in a 3-D stack, showed that 1) the thermal impact of stacking memories on microprocessors is not significant [64], and power consumption of a large memory can be reduced with a proper 3-D floor-planning [59]; and 2) 3-D implementation can improve power, clock frequency, temperature, and performance for a given system. For example, in a 3-D logic-to-logic stack of two strata, scaling to neutral performance yields a 54% power reduction; or frequency and voltage scaling can produce a 34% power reduction with 8% performance improvement; or a simultaneous 15% performance gain and 15% power reduction can be achieved [65]. This 3-D benefit in temperature and power is mainly due to significant reduction in long interconnects and the number of associated repeaters (note: 2-3 million repeaters may be required for a 2-D processor designed at 45 nm [86]). Typically a power reduction results in a performance reduction, but in the 3-D design the energy consumed per instruction is reduced without reducing performance.

Three-dimensional platforms provide more design space, allowing a greater range of performance and power tradeoffs while making other thermal and power management possible, such as 3-D power delivery [73], [74] and integration of microfluidic channels for heat removal [87], [88].

#### **D.** Infrastructure Challenges

As with any disruptive technology introduced to highvolume manufacturing, 3-D hyperintegration requires:

- equipment for 24/7 operation;

- ECAD and simulation tools;

- standards.

Most processing equipment and tools needed for 3-D integration are listed in Table 3. These tools have been available for years and used in product manufacturing. However, the aligner, bonder and deep via (TSV) etcher do not meet the requirements of the IC industry for high-volume 24/7 manufacturing of 3-D systems. The TSV technology being developed for 3-D packaging can be readily modified for wafer-level 3-D integration. In addition, the wafer bonding processes developed to date can take an hour or more; shorter process times are certainly desirable, maybe with cluster tools. Other process requirements are technology platform dependent as described earlier.

Two-dimensional ECAD and simulation tools are currently used for 3-D integration with some modifications, while the research and development of 3-D design and simulations tools shows good progress [55]–[81], [93]. Significant developments in ECAD and simulation tools are required to: 1) allow use of mixed technology nodes and mixed processing technologies (such as for silicon or compound semiconductor, analog, digital, various types of memories) with abundant IP cores, 2) effectively utilize the 3-D advantages in smaller die size, massive short vertical interstrata interconnects, and huge data bandwidth, 3) provide the flexibility for novel circuit designs that are impossible with 2-D circuits, 4) establish design rules, particularly for certain circuits that may not be complete in one circuit stratum, 5) include yield enhancements (e.g., redundancy, ECC, DFT, and BIST), and 6) accommodate thermal and power constraints. These will require simulation software to ensure signal and power integrity with semiconductor devices in multiple strata.

Besides equipment and ECAD tools, one very critical infrastructure development for 3-D integration is to establish a set of standards; little has been done so far. It is very critical because 1) various materials and processing technologies are involved and 2) die or wafers can come from different IC manufacturers in different sectors of industry; even the die or wafer sizes can be different. While SEMATECH has attempted to develop a roadmap within the International Technology Roadmap for Semiconductors (ITRS) [89], a new association or society perhaps should be formed in order to establish 3-D integration standards and roadmaps.

# VI. 3-D INTEGRATION PERSPECTIVES

Jack Kilby invented the integrated circuit (IC) in 1958 at Texas Instruments. About ten years later, Intel introduced the world's first single-chip microprocessor, the Intel 4004, in 1971. We have since then experienced an exponential growth of ICs following Moore's law in terms of transistor numbers per chip. Both the bipolar transistor and MOS field-effect transistor were the workhorses for about two decades. Since 1990, CMOS has become the predominant technology in digital ICs because of benefits in the areas of circuit size, operating speed, energy efficiency, and manufacturing costs. The major issue that led to the switch from bipolar transistors to CMOS was that the thermal power density of bipolar ICs reached a level that was extremely difficult to cool. After enjoying CMOS technology for little more than ten years, we have encountered again the thermal power issue, as marked perhaps by Intel pulling the plug on a planned 4.0-GHz speed upgrade of its Pentium 4 processor in late 2004. We then entered into an era of single-chip multicore processors [82]-[84], [90]. Since the multicore processor requires huge cache capacity and memory bandwidth, 3-D integration is perhaps the only viable solution to provide the required cache and bandwidth. Considering the profound impact of the semiconductor industry on our business, economics, and society, the author believes that we will soon enter into a new era of 3-D hyperintegration of infotech, nanotech, and biotech systems-a new paradigm for future technologies, as depicted in Fig. 1.

Looking forward, the first killer 3-D applications would be extremely high-density heterogeneous memory stacks (e.g., NAND flash, SRAM, DRAM, FRAM, and PCNVM) and extremely high-resolution/low-cost imagers, followed perhaps by 3-D integration of mixed signal/RF circuits with digital CMOS. Advanced handheld devices will also continue to drive the mix and match of various 3-D approaches.

A variety of 3-D approaches may be combined to offer more flexible integration with even higher functionality, signal integrity, or added value. For example, stacking discrete die (or discrete devices, such as solid-state lasers or GaN transistors) onto a wafer stack provides a pathway for heterogeneous integration of compound semiconductor devices or analog circuits with digital circuits.

Once 3-D integration technology is mature and the design and manufacturing infrastructure (such as ECAD tools, fabrication equipment, and standards) is in place, it is likely that more ICs will be designed for general purposes because massive production of 3-D ICs would lower the manufacturing cost. For instance, a general-purpose 3-D multicore processor with extremely high-density memory, FPGA, and software in the nonvolatile memory in the same stack could be reprogrammed by FPGA or software for multiple purposes, or varying purposes, over a processor's lifetime. We might even have to change the term of "3-D hyperintegration" to "4-D hyperintegration" because the highly integrated system can be changed with the fourth dimension, i.e., time. An example would be using PCNVM to change an FPGA or to reroute different processor cores in the same stack if needed at certain times.

As shown in Fig. 1, ongoing research and development in 3-D integration could lead to a new paradigm of future technologies for hyperintegration of infotech-nanotechbiotech systems, enabling extremely high functionality, high performance, and small size and weight with very low cost. Different components optimized for energy/power can be integrated, such as processors, memories, imagers, wireless communications, special functions of nanodevices and MEMS, various micro/nanoscale chemical, bio, thermal, mechanical, electrical, and optical sensors, and even nuclear (radiation) sensors. Different industry sectors, universities, and government may have to reshape their business models to meet the required close collaborations in building more highly integrated systems. In the future, it will not be just a dream that a tiny device can fly, move, see, smell, hear, taste/analyze, feel, and "think"; it will be able to interact with other devices and with human beings and their surroundings; it could perform certain functions, such as for security (e.g., detection of dangerous materials, devices, or terrorists) and health care (e.g., medical devices and drug discovery). Our daily lifestyle and even our culture may be dramatically changed with a proliferation of this 3-D or 4-D hyperintegration technology.

# Acknowledgment

The author gratefully acknowledges faculty colleagues, postdoctoral associates, and graduate students for their contributions to the RPI 3-D hyperintegration research programs and for their comments and discussions since 1999, including faculty members of Prof. T. S. Cale, Prof. R. J. Gutmann, Prof. M. Hella, Prof. T.-M. Lu, Prof. J. F. McDonald, Prof. P. D. Persans, Prof. K. Rose, Prof. J. Sun, and Prof. T. Zhang; visiting scientists and postdoctoral associates of Dr. A. Jindal, Dr. R. J. Kumar, Dr. K. Lee, Dr. S. H. Lee, Dr. Z. Liu, Dr. F. Niklaus, and Dr. G. Zhang; and Graduate Students of Dr. S. Devarajan, D. Giuliano, Dr. Y. Kwon, Dr. J. J. McMahon, Dr. J. Yu,

#### REFERENCES

- J.-Q. Lu, K. Rose, and S. Vitkavage, "3D integration: Why, what, who, when?" *Future Fab Int.*, no. 23, pp. 25–27, Jul. 2007.

- [2] C.-G. Hwang, "New paradigms in the silicon industry," in Tech. Dig. IEEE Int. Electron Devices Meeting (2006 IEDM), Dec. 2006, pp. 19–26.

- [3] F. Carson, "3D SiP developments and trends," in 3D Packag. Workshop IMAPS Int. Conf. Exhib. Device Packag. Conf., Scottsdale, AZ, Mar. 2007.

- [4] M. Dreiza, A. Yoshida, K. Ishibashi, and T. Maeda, "High density PoP (package-on-package) and package stacking development," in Proc. 57th Electron. Compon. Technol. Conf. (ECTC 2007), Jun. 2007, pp. 1379–1402.

- [5] K. Lee, "The next generation package technology for higher performance and smaller systems," in Proc. 3rd Int. Conf. 3D Architect. Semicond. Integr. Packag., Burlingame, CA, Oct. 31–Nov. 2, 2006.

- [6] S. Spiesshoefer, Z. Rahman, G. Vangara, S. Polamreddy, S. Burkett, and L. Schaper, "Process integration for through-silicon vias," *J. Vac. Sci. Technol. A*, vol. 23, no. 4, pp. 824–829, Jul./Aug. 2005.

- [7] M. Bonkohara, "3D stacked LSI interconection by Cu-Vias & 3D system integration," in Proc. 3D Architect. Semicond. Integr. Packag., Burlingame, CA, Apr. 2004.

- [8] B. Markunas, "3D technology: Early market opportunities," in Proc. 3D Architect. Semicond. Integr. Packag., Tempe, AZ, Jun. 2005.

- [9] A. Klumpp, R. Merkel, P. Ramm, J. Weber, and R. Wieland, "Vertical system integration by using inter-chip vias and solid-liquid interdiffusion bonding," *Ipn. J. Appl. Phys.*, vol. 43, no. 7A, pp. L829–L830, 2004.

- [10] K. Banerjee, S. J. Souri, P. Kapur, and K. C. Saraswat, "3-D ICs: A novel chip design for improving deep-submicrometer interconnect performance and systems-on-chip integration," *Proc. IEEE*, vol. 89, pp. 602–633, May 2001.

- [11] M. Crowley, A. Al-Shamma, D. Bosch, M. Farmwald, L. Fasoli, A. Ilkbahar, M. Johnson, B. Kleveland, T. Lee, T.-Y. Liu, Q. Nguyen, R. Scheuerlein, K. So, and T. Thorp, "512 Mb PROM with 8 layers of antifuse/diode cells," in *Proc. 2003 IEEE Int. Solid-State Circuits Conf. (ISSCC 2003)*, 2003, vol. 1, pp. 284–493.

- [12] S.-M. Jung, J. Jang, W. Cho, J. Moon, K. Kwak, B. Choi, B. Hwang, H. Lim, J. Jeong, J. Kim, and K. Kim, "The revolutionary and truly 3-dimensional 25F2 SRAM technology with the smallest S3 (stacked single-crystal Si) cell, 0.16 μm<sup>2</sup>, and SSTFT (stacked single-crystal thin film transistor) for ultra high density SRAM," in *Proc. 2004 Symp. VLSI Technol.*, Jun. 15–17, 2004, pp. 228–229.

- [13] S.-M. Jung, J. Jang, and K. Kim, "Three dimensionally stacked NAND flash memory technology using stacked single crystal Si layers in ILD and TANOS structure for beyond 30 nm node," in *Tech. Dig. IEEE Int. Electron Devices Meeting (2006 IEDM)*, Dec. 2006, pp. 37–40.

- [14] P. Garrou, P. Ramm, and C. Bower, Eds., Handbook of 3D Integration: Technology and Applications of 3D Integrated Circuits. New York: Wiley-VCN, May 2008.

- [15] J.-Q. Lu, T. S. Cale, and R. J. Gutmann, "Wafer-level three-dimensional hyper-integration technology using dielectric adhesive wafer bonding," in Materials for Information Technology: Devices, Interconnects and Packaging, E. Zschech, C. Whelan, and T. Mikolajick, Eds. London, U.K.: Springer-Verlag, Aug. 2005, pp. 386–397.

- [16] J. J. McMahon, J.-Q. Lu, and R. J. Gutmann, "Wafer bonding of Damascene-patterned metal/adhesive redistribution layers for via-first 3D interconnect," in *Proc. 55th IEEE Electron. Compon. Technol. Conf. (ECTC 2005)*, 2005, pp. 331–336.

- [17] R. J. Gutmann, J. J. McMahon, and J.-Q. Lu, "Damascene patterned metal/adhesive redistribution layers," in *Enabling Technologies for 3-D Integration*, vol. 970, C. A. Bower, P. E. Garrou, P. Ramm, and K. Takahashi, Eds. Warrendale, PA: Materials Research Society, 2007.

- [18] J.-Q. Lu, A. Jindal, Y. Kwon, J. J. McMahon, M. Rasco, R. Augur, T. S. Cale, and R. J. Gutmann, "Evaluation procedures for wafer bonding and thinning of interconnect test structures for 3D ICs," in *Proc. 2003 IEEE Int. Interconnect Technol. Conf. (IITC 2003)*, Jun. 2003, pp. 74–76.

- [19] R. J. Gutmann, J.-Q. Lu, S. Pozder, Y. Kwon, D. Menke, A. Jindal, M. Celik, M. Rasco, J. J. McMahon, K. Yu, and T. S. Cale, "A wafer-level 3D IC technology platform," in Proc. Adv. Metal. Conf. 2003 (AMC 2003), 2003, pp. 19–26.

- [20] S. Pozder, J.-Q. Lu, Y. Kwon, S. Zollner, J. Yu, J. J. McMahon, T. S. Cale, K. Yu, and R. J. Gutmann, "Back-end compatibility of bonding and thinning processes for a wafer-level 3D interconnect technology platform," in *Proc. 2004 IEEE Int. Interconnect Technol. Conf. (IITC 2004)*, Jun. 2004, pp. 102–104.

- [21] J.-Q. Lu, Y. Kwon, R. P. Kraft, R. J. Gutmann, J. F. McDonald, and T. S. Cale, "Stacked chip-to-chip interconnections using wafer bonding technology with dielectric bonding glues," in *Proc. 2001 IEEE Int. Interconnect Technol. Conf. (IITC 2001)*, Jun. 4–6, 2001, pp. 219–221.

- [22] J.-Q. Lü, A. Kumar, Y. Kwon, E. T. Eisenbraun, R. P. Kraft, J. F. McDonald, R. J. Gutmann, T. S. Cale, P. Belemjain, O. Erdogan, J. Castracane, and

- A. E. Kaloyeros, "3-D integration using wafer bonding," in Proc. Adv. Metal. Conf. 2000

and Dr. A. Zeng. Particular thanks go to Prof. K. Rose for his extensive discussions of this manuscript. Many offcampus colleagues and friends are also greatly acknowledged for their contributions to RPI's 3-D research programs and their collaborations, comments, and discussions over the years, particularly those from AMD, Dow Chemical, EVGroup, IBM, Intel, Freescale, Georgia Institute of Technology, MIT, Motorola, Samsung, SEMATECH, Stanford, University at Albany, and funding agencies.

> (AMC 2000), vol. V16, D. Edelstein, G. Dixit, Y. Yasuda, and T. Ohba, Eds., 2001, vol. V16, pp. 515–521.

- [23] K.-N. Chen, S. H. Lee, P. S. Andry, C. K. Tsang, A. W. Topol, Y.-M. Lin, J.-Q. Lu, A. M. Young, M. Ieong, and W. Haensch, "Structure design and process control for Cu bonded interconnects in 3D integrated circuits," in *Tech. Dig. IEEE Int. Electron Devices Meeting (2006 IEDM)*, Dec. 2006, pp. 367–370.

- [24] K. W. Guarini, A. W. Topol, M. Ieong, R. Yu, L. Shi, M. R. Newport, D. J. Frank, D. V. Singh, G. M. Cohen, S. V. Nitta, D. C. Boyd, P. A. O'Neil, S. L. Tempest, H. B. Pogge, S. Purushothaman, and W. E. Haensch, "Electrical integrity of state-of-the-art 0.13 mm SOI CMOS devices and circuits transferred for three-dimensional (3D) integrated circuit (IC) fabrication," in Tech. Dig. IEEE Int. Electron Devices Meeting (2002 IEDM), 2002, pp. 943–945.

- [25] J. Burns, L. McIlrath, C. Keast, A. Loomis, K. Warner, and P. Wyatt, "Three-dimensional integrated circuits for low-power, high-bandwidth systems on a chip," in *Proc. 2001 IEEE Int. Solid-State Circuits Conf.* (ISSCC 2001), 2001, pp. 268–269, 453.

- [26] J. A. Burns, B. F. Aull, C. K. Chen, C.-L. Chen, C. L. Keast, J. M. Knecht, V. Suntharalingam, K. Warner, P. W. Wyatt, and D.-R. W. Yost, "A wafer-scale 3-D circuit integration technology," *IEEE Trans. Electron Devices*, vol. 53, pp. 2507–2516, Oct. 2006.

- [27] A. Fan, K. N. Chen, and R. Reif, "Three-dimensional integration with copper wafer bonding," in Proc. Electrochem. Soc. ULSI Process Integr. Symp., 2001, pp. 124–128.

- [28] K. N. Chen, A. Fan, C. S. Tan, and R. Reif, "Microstructure evolution and abnormal grain growth during copper wafer bonding," *Appl. Phys. Lett.*, vol. 81, no. 20, pp. 3774–3776, 2002.

- [29] R. Patti, "Three-dimensional integrated circuits and the future of system-on-chip designs," *Proc. IEEE*, vol. 94, no. 6, pp. 1214–1222, 2006.

- [30] P. Morrow, C.-M. Park, S. Ramanathan, M. J. Kobrinsky, and M. Harmes, "Three-dimensional wafer stacking via Cu-Cu bonding integrated with 65-nm strained-Si/low-k CMOS technology," *IEEE Electron Device Lett.*, vol. 27, no. 5, pp. 335–337, 2006.

- [31] P. Morrow, B. Black, M. J. Kobrinsky, S. Muthukumar, D. Nelson, C.-M. Park, and C. Webb, "Design and fabrication of 3D microprocessors," in *Enabling Technologies* for 3-D Integration, vol. 970, C. A. Bower, P. E. Garrou, P. Ramm, and K. Takahashi, Eds. Warrendale, PA: Materials Research Society, 2007.

- [32] P. Ramm, D. Bonfert, H. Gieser, J. Haufe, F. Iberl, A. Klumpp, A. Kux, and R. Wieland, "InterChip via technology for vertical system integration," in *Proc. IEEE Int.*

Interconnect Technol. Conf. 2001 (IITC 2001), 2001, pp. 160–162.

- [33] K. W. Lee, T. Nakamura, T. One, Y. Yamada, T. Mizukusa, H. Hasimoto, K. T. Park, H. Kurino, and M. Koyanagi, "Three dimensional shared memory fabricated using wafer stacking technology," in *Tech. Dig. IEEE Int. Electron Devices Meeting (2000 IEDM)*, 2000, pp. 165–168.

- [34] M. Bonkohara, M. Motoyoshi, K. Kamibayashi, and M. Koyanagi, "Current and future three-dimensional LSI integration technology by 'chip on chip', 'chip on wafer' and 'wafer on wafer'," in *Enabling Technologies for 3-D Integration*, vol. 970, C. A. Bower, P. E. Garrou, P. Ramm, and K. Takahashi, Eds. Warrendale, PA: Materials Research Society, 2007.

- [35] B. Charlet, "3-D integration latest developments at LETI," in *Enabling Technologies for 3-D Integration*, vol. 970, C. A. Bower, P. E. Garrou, P. Ramm, and K. Takahashi, Eds. Warrendale, PA: Materials Research Society, 2007.

- [36] P. De Moor, W. Ruythooren, P. Soussan, B. Swinnen, K. Baert, C. Van Hoof, and E. Beyne, "Recent advances in 3D integration at IMEC," in *Enabling Technologies for 3-D Integration*, vol. 970, C. A. Bower, P. E. Garrou, P. Ramm, and K. Takahashi, Eds. Warrendale, PA: Materials Research Society, 2007.

- [37] S. Pozder, R. Jones, V. Adams, H.-F. Li, M. Canonico, S. Zollner, S. H. Lee, R. J. Gutmann, and J.-Q. Lu, "Exploration of the scaling limits of 3D integration," in *Enabling Technologies for 3-D Integration*, vol. 970, C. A. Bower, P. E. Garrou, P. Ramm, and K. Takahashi, Eds. Warrendale, PA: Materials Research Society, 2007.

- [38] B. Kim, "Through-silicon-via copper deposition for vertical chip integration," in *Enabling Technologies for 3-D Integration*, vol. 970, C. A. Bower, P. E. Garrou, P. Ramm, and K. Takahashi, Eds. Warrendale, PA: Materials Research Society, 2007.

- [39] T. Matthias, M. Wimplinger, S. Pargfrieder, and P. Lindner, "3D process integration—Wafer-to-wafer and chip-to-wafer bonding," in *Enabling Technologies for 3-D Integration*, vol. 970, C. A. Bower, P. E. Garrou, P. Ramm, and K. Takahashi, Eds. Warrendale, PA: Materials Research Society, 2007.

- [40] K. Gann, "Neo-stacking technology," High Density Interconnect Mag., vol. 2, Dec. 1999.

- [41] J. U. Knickerbocker, P. S. Andry, L. P. Buchwalter, E. G. Colgan, J. Cotte, H. Gan, R. R. Horton, S. M. Sri-Jayantha, J. H. Magerlein, D. Manzer, G. McVicker, C. S. Patel, R. J. Polastre, E. S. Sprogis, C. K. Tsang, B. C. Webb, and S. L. Wright, "System-on-package (SOP) technology, characterization and applications," in Proc. 56th IEEE Electron. Compon. Technol. Conf. (ECTC 2006), 2006, pp. 415–421.

- [42] P. Enquist, "Bond interconnect (DBI)—Technology for scalable 3D SoCs," in Proc. 3rd Int. Conf. 3D Architect. Semicond. Integr. Packag., Burlingame, CA, Oct. 31–Nov. 2, 2006.

- [43] J.-Q. Lu, Y. Kwon, G. Rajagopalan, M. Gupta, J. McMahon, K.-W. Lee, R. P. Kraft, J. F. McDonald, T. S. Cale, R. J. Gutmann, B. Xu, E. Eisenbraun, J. Castracane, and A. Kaloyeros, "A wafer-scale 3D IC technology platform using dielectric bonding glues and copper damascene patterned inter-wafer interconnects," in *Proc. IEEE Int. Interconnect Technol. Conf. (IITC 2002)*, San Francisco, CA, Jun. 2002, pp. 78–80.

- [44] M. Wimplinger, J.-Q. Lu, J. Yu, Y. Kwon, T. Matthias, T. S. Cale, and R. J. Gutmann, "Fundamental limits for 3D wafer-to-wafer alignment accuracy," in Materials, Technology, Reliability for Advanced Interconnects and Low-k Dielectrics, vol. 812, R. J. Carter, C. S. Hau-Riege, G. M. Kloster, T.-M. Lu, and S. E. Schulz, Eds. Warrendale, PA: Materials Research Society, 2004, pp. F6.10.1–F6.10.6.

- [45] J.-Q. Lu, K. W. Lee, Y. Kwon, G. Rajagopalan, J. McMahon, B. Altemus, M. Gupta, E. Eisenbraun, B. Xu, A. Jindal, R. P. Kraft, J. F. McDonald, J. Castracane, T. S. Cale, A. Kaloyeros, and R. J. Gutmann, "Processing of inter-wafer vertical interconnects in 3D ICs," in *Proc. Adv. Metal. Conf. 2002* (*AMC 2002*), vol. V18, *MRS*, B. M. Melnick, T. S. Cale, S. Zaima, and T. Ohta, Eds., 2003, pp. 45–51.

- [46] S. H. Lee, F. Niklaus, J. J. McMahon, J. Yu, R. J. Kumar, H.-F. Li, R. J. Gutmann, T. S. Cale, and J.-Q. Lu, "Fine keyed alignment and bonding for wafer-level 3D ICs," in Materials, Technology and Reliability of Low-k Dielectrics and Copper Interconnects, vol. 914, T. Y. Tsui, Y.-C. Joo, A. A. Volinsky, M. Lane, and L. Michaelson, Eds. Warrendale, PA: Materials Research Society, 2006, p. 0914-F10-05.

- [47] F. Niklaus, G. Stemme, J.-Q. Lu, and R. Gutmann, "Adhesive wafer bonding," *J. Appl. Phys.*, vol. 99, no. 3, pp. 031101-1–031101-28, Feb. 1, 2006.

- [48] Y. Kwon, J. Seok, J.-Q. Lu, T. S. Cale, and R. J. Gutmann, "Thermal cycling effects on critical adhesion energy and residual stress in benzocyclobutene (BCB)-bonded wafers," J. Electrochem. Soc., vol. 152, no. 4, pp. G286–G294, Mar. 2005.

- [49] Y. Kwon, J. Seok, J.-Q. Lu, T. S. Cale, and R. J. Gutmann, "Critical adhesion energy of benzocyclobutene (BCB)-bonded wafers," J. Electrochem. Soc., vol. 153, no. 4, pp. G347–G352, Feb. 2006.

- [50] J. Yu, Y. Wang, J.-Q. Lu, and R. J. Gutmann, "Low-temperature silicon wafer bonding based on Ti/Si solid-state amorphization," *Appl. Phys. Lett.*, vol. 89, p. 092104, Aug. 2006.

- [51] J. Yu, Y. Wang, R. L. Moore, J.-Q. Lu, and R. J. Gutmann, "Low-temperature titanium-based wafer bonding: Ti/Si, Ti/SiO2, and Ti/Ti," J. Electrochem. Soc., vol. 154, no. 1, pp. H20-H25, 2007.

- [52] R. Wieland, D. Bonfert, A. Klumpp, R. Merkel, L. Nebrich, J. Weber, and P. Ramm, "3D integration of CMOS transistors with ICV-SLID technology," *Microelectron. Eng.*, vol. 82, pp. 529–33, 2005.

- [53] B. Swinnen, W. Ruythooren, P. De Moor, L. Bogaerts, L. Carbonell, K. De Munck, B. Eyckens, S. Stoukatch, D. Sabuncuoglu Tezcan, Z. Tokei, J. Vaes, J. Van Aelst, and E. Beyne, "3D integration by Cu-Cu thermo-compression bonding of extremely thinned bulk-Si die containing 10 μm pitch through-Si vias," in *Tech. Dig. IEEE Int. Electron Devices Meeting (2006 IEDM)*, Dec. 2006, pp. 271–374, IEEE.

- [54] J.-Q. Lu, J. J. McMahon, and R. J. Gutmann, "Via-first inter-wafer vertical interconnects utilizing wafer-bonding of damascene-patterned metal/adhesive redistribution layers," in 3D Packag. Workshop IMAPS Device Packag. Conf., Scottsdale, AZ, Mar. 20–23, 2006.

- [55] J. D. Meindl, J. A. Davis, P. Zarkesh-Ha, C. S. Patel, K. P. Martin, and P. A. Kohl, "Interconnect opportunities for gigascale

research," IBM J. Res. Develop., vol. 46, no. 2/3, pp. 245–263, 2002.

- [56] J. D. Meindl, R. Venkatesan, J. A. Davis, J. W. Joyner, A. Naeemi, P. Zarkesh-Ha, M. Bakir, T. Mulé, P. A. Kohl, and K. P. Martin, "Interconnecting device opportunities for gigascale integration (GSI)," in Tech. Dig. IEEE Int. Electron Devices Meeting (2001 IEDM), 2001, pp. 525–528.

- [57] J. W. Joyner and J. D. Meindl, "Opportunities for reduced power dissipation using three-dimensional integration," in *Proc. 2002 IEEE Int. Interconnect Technol. Conf. (IITC02)*, Jun. 2002, pp. 148–150.

- [58] S. Das, A. Fan, K.-N. Chen, C. S. Tan, N. Checka, and R. Reif, "Technology, performance, and computer-aided design of three-dimensional integrated circuits," in *Proc. Int. Symp. Phys. Design*, 2004, pp. 108–115.

- [59] A. Y. Zeng, J.-Q. Lu, K. Rose, and R. J. Gutmann, "First-order performance prediction of cache memory with wafer-level 3D integration," *IEEE Design Test Comput.*, vol. 22, pp. 548–555, Nov./Dec. 2005.

- [60] M. Bamal, S. List, M. Stucchi, A. S. Verhulst, M. Van Hove, R. Cartuyvels, G. Beyer, and K. Maex, "Performance comparison of interconnect technology and architecture options for deep submicron technology nodes," in *Proc. IEEE Int. Interconnect Technol. Conf. (IITC 2006)*, Jun. 2006, pp. 202–204.

- [61] C. C. Liu, I. Ganusov, M. Burtscher, and S. Tiwari, "Bridging the processor-memory performance gap with 3D IC technology," *IEEE Design Test Comput.*, vol. 22, no. 6, pp. 556–564, 2005.

- [62] A. Y. Zeng, K. Rose, and R. J. Gutmann, "Memory performance prediction for high-performance microprocessors at deep submicrometer technologies," *IEEE Trans. Computer-Aided Design Integr. Circuits Syst.*, vol. 25, pp. 1705–1718, Sep. 2006.

- [63] K. Bernstein, "New directions in performance—Emerging 3D integration technologies," in Keynote Address 23rd Int. VLSI Multilevel Interconnect. (VMIC) Conf., Sep. 2006.

- [64] B. Black, D. W. Nelson, C. Webb, and N. Samra, "3D processing technology and its impact on iA32 microprocessors," in *Proc. IEEE Int. Conf. Computer Design*, 2004, pp. 316–318.

- [65] B. Black, M. Annavaram, N. Brekelbaum, J. DeVale, L. Jiang, G. H. Loh, D. McCauley, P. Morrow, D. W. Nelson, D. Pantuso, P. Reed, J. Rupley, S. Shankar, J. Shen, and C. Webb, "Die stacking (3D) microarchitecture," in *Proc. 39th Annu. IEEE/ACM Int. Symp. Microarchitect.* (*MICRO*), Dec. 2006, pp. 469–479.

- [66] K. Puttaswamy and G. H. Loh, "The impact of 3-dimensional integration on the design of arithmetic units," in Proc. IEEE Int. Symp. Circuits Syst., May 2006, pp. 4951–4954.

- [67] W. R. Davis, J. Wilson, S. Mick, J. Xu, H. Hua, C. Mineo, A. M. Sule, M. Steer, and P. D. Franzon, "Demystifying 3D ICs: The pros and cons of going vertical," *IEEE Design Test Comput.*, vol. 22, no. 6, pp. 498–510, 2005.

- [68] C. Ababei, Y. Feng, B. Goplen, H. Mogal, T. Zhang, K. Bazargan, and S. Sapatnekar, "Placement and routing in 3D integrated circuits," *IEEE Design Test Comput.*, vol. 22, no. 6, pp. 520–531, 2005.

- [69] A. Rahman, S. Das, A. P. Chandrakasan, and R. Reif, "Wiring requirement and three-dimensional integration technology

for field programmable gate arrays," *IEEE Trans. VLSI Syst.*, vol. 11, no. 1, pp. 44–54, 2003.

- [70] D. Temple, C. A. Bower, D. Malta, J. E. Robinson, P. R. Coffman, M. R. Skokan, and T. B. Welch, "High density 3-D integration technology for massively parallel signal processing in advanced infrared focal plane array sensors," in *Tech. Dig. IEEE Int. Electron Devices Meeting (2006 IEDM)*, Dec. 2006, pp. 143–146.

- [71] R. J. Gutmann, A. Y. Zeng, S. Devarajan, J.-Q. Lu, and K. Rose, "Wafer-level three-dimensional monolithic integration for intelligent wireless terminals," *J. Semicond. Technol. Sci.*, vol. 4, no. 3, pp. 196–203, Sep. 2004.

- [72] J.-Q. Lu, S. Devarajan, A. Y. Zeng, K. Rose, and R. J. Gutmann, "Die-on-wafer and wafer-level three-dimensional (3D) integration of heterogeneous IC technologies for RF-microwave-millimeter applications," in Materials, Integration and Packaging Issues for High-Frequency Devices II, vol. 833, Y. S. Cho, D. Shiffler, C. A. Ranall, H. A. C. Tilmans, and T. Tsurumi, Eds. Warrendale, PA: Materials Research Society, 2004, pp. G6.8.1–G6.8.6.

- [73] J.-Q. Lu, J. Sun, D. Giuliano, and R. J. Gutmann, "3D architecture for power delivery to microprocessors and ASICs," in Proc. 3rd Int. Conf. 3D Architect. Semicond. Integr. Packag., Burlingame, CA, Oct. 31–Nov. 2, 2006.

- [74] J. Sun, J.-Q. Lu, D. Giuliano, P. Chow, and R. J. Gutmann, "3D power delivery for microprocessors and high-performance ASICs," in Proc. 22nd Annu. IEEE Applied Power Electronics Conf. Expo. (APEC 2007), 2007, pp. 127–133.

- [75] L. McIlrath, "CAD tools for 3D system design," in Proc. 3rd Int. Conf. 3D Architect. Semicond. Integr. Packag., Burlingame, CA, Oct. 31-Nov. 2, 2006.

- [76] G. Loh, Y. Xie, and B. Black, "Processor design in three-dimensional die-stacking technologies," *IEEE Micro*, vol. 27, pp. 31–48, May/Jun. 2007.

- [77] J. C. Kim, C. Nicopoulos, D. Park, R. Das, Y. Xie, N. Vijaykrishnan, and C. R. Das, "A novel dimensionally-decomposed router for on-chip communication in 3D architectures," in *Proc. Annu. Int. Symp. Comput. Architect. (ISCA)*, Jun. 2007, pp. 138–149.

- [78] Y. Xie, G. Loh, B. Black, and K. Bernstein, "Design space exploration for 3D architecture," ACM J. Emerging Technol. Comput. Syst., vol. 2, no. 2, pp. 65–103, Apr. 2006.

- [79] J. Cong and Y. Zhang, "Thermal via planning for 3-D ICs," in Proc. 2005 IEEE/ACM Int. Conf. Computer-Aided Design (ICCAD 2005), Nov. 6-10, 2005, pp. 745-752.

- [80] J. Cong, G. Luo, J. Wei, and Y. Zhang, "Thermal-aware 3D IC placement via transformation," in Proc. 12th Asia South Pacific Design Autom. Conf. (ASP-DAC 2007), Yokohama, Japan, Jan. 2007, pp. 780–785.

- [81] J. Zhang, M. O. Bloomfield, J.-Q. Lu, R. J. Gutmann, and T. S. Cale, "Modeling thermal stresses in 3-D IC interwafer interconnects," *IEEE Trans. Semicond. Manuf.*, vol. 19, pp. 437–448, Nov. 2006.

- [82] S. Rusu, S. Tam, H. Muljono, D. Ayers, and J. Chang, "A dual-core multi-threaded Xeon(r) processor with 16 Mb L3 cache," in Proc. 2006 IEEE Int. Solid-State Circuits Conf. (ISSCC 2006), Feb. 2006, pp. 315–324.

- [83] S. Rusu, S. Tam, H. Muljono, D. Ayers, J. Chang, B. Cherkauer, J. Stinson, J. Benoit, R. Varada, J. Leung, R. D. Limaye, and S. Vora, "A 65-nm dual-core MultiThreaded Xeon processor with 16 Mb L-3 cache," *IEEE J. Solid-State Circuits*, vol. 42, pp. 17–25, Jan. 2007.

- [84] L. Bushard, N. Chelstrom, S. Ferguson, and B. Keller, "Testing challenges of a multicore microprocessor," *Eval. Eng.*, vol. 46, no. 2, pp. 12f, Feb. 2007.

- [85] E. Sperling, "Turn down the heat . . . please," Tom Reeves IBM VP Interviews, Electron. News, Jul. 7, 2006.

- [86] R. Puri, "3D design and CAD challenges," presented at the SEMATECH Workshop Thermal Design Issues 3-D ICs, Oct. 11–12, 2007.

- [87] B. Dang, M. S. Bakir, and J. D. Meindl, "Integrated thermal-fluidic I/O interconnects for an on-chip microchannel heat sink,"

IEEE Electron Device Lett., vol. 27, no. 2, pp. 117–119, 2006.

- [88] J. M. Koo, S. Im, L. Jiang, and K. E. Goodson, "Integrated microchannel cooling for three-dimensional circuit architectures," *ASME J. Heat Transfer*, vol. 127, pp. 49–58, Jan. 2005.

- [89] Semiconductor Industry Association. International Technology Roadmap for Semiconductors, 2005. [Online]. Available: http://www.public.itrs.net/

- [90] S. Vangal, J. Howard, G. Ruhl, S. Dighe, H. Wilson, J. Tschanz, D. Finan, P. Iyer, A. Singh, T. Jacob, S. Jain, S. Venkataraman, Y. Hoskote, and N. Borkar, "An 80-tile 1.28 TFLOPS network-on-chip in 65 nm CMOS," in Proc. 2007 IEEE Int. Solid-State Circuit Conf. (ISSCC 2007), Feb. 2007, pp. 98–99, 589.

- [91] L. Smith, "Package-on-package: The story behind this industry hit," Semicond. Int. Mag., Jun. 2007.

- [92] V. Subramanian and K. Saraswat, "High performance germanium-seeded laterally crystallized TFT's for vertical device integration," *IEEE Trans. Electron Devices*, vol. 45, pp. 1934–1939, Sep. 1998.

- [93] J. W. Joyner, P. Zarkesh-Ha, and J. D. Meindl, "A global interconnect design window for a three-dimensional system-on-a-chip," in *Tech.* Dig. IEEE Int. Electron Devices Meeting (2001 IEDM), 2001, pp. 154–156.

#### ABOUT THE AUTHOR

Jian-Qiang (James) Lu (Senior Member, IEEE) received the Dr.rer.nat. (Ph.D.) degree from Technical University of Munich, Germany, in 1995.

He is an Associate Professor at Rensselaer Polytechnic Institute, where he has been working on the Interconnect Focus Center (IFC) flagship research program of 3-D hyperintegration technology since 1999, and several other programs with focus on hyper-integration and micro-nano-bio interfaces for future chips. Prior to 1999, he held research and faculty positions with a number of universities in China, Germany and the United States.

He has broad research experiences from micro-nano-electronics theory and design to materials, processing, devices, integration and packaging (e.g., Si, GaAs, and GaN devices, novel field-effect transistors, terahertz electronics, carbon-nanotubes, and Si IC interconnects). His current research interests include 3-D hyperintegration design and technology, and micro-nano-bio interfaces for future chips and microelectromechanical systems. He has authored/coauthored more than 180 publications in refereed journals, conferences, or books, and given a number of invited presentations, seminars and short courses. He has served as a Technical Chair, Workshop Chair, Session Chair, Panelist, and Panel Moderator for many conferences.

Dr. Lu is a member of the American Physics Society, Materials Research Society, and Electrochemical Society. He is a member of the National Technical Committee (Chair of 3D Packaging) for the International Microelectronics and Packaging Society. He received an "IEEE CPMT Exceptional Technical Achievement Award" in May 2008 "for his pioneering contributions to and leadership in 3D integration/packaging."