# On Dissipativity Conditions for Linearized Models of Locally Active Circuit Blocks

T. Bradde\*, S. Grivet-Talocia\*, G. C. Calafiore\*, A. V. Proskurnikov\*, Z. Mahmood<sup>†</sup>, L. Daniel<sup>‡</sup>

\* Dept. Electronics and Telecommunications, Politecnico di Torino, Italy

† NanoSemi, Inc., USA

Abstract—This paper generalizes the concept of dissipativity of linear models to linearized models of nonlinear circuit blocks that may also include locally active behavior. We show that such models can be guaranteed to behave as dissipative, provided they are subjected to certain bounds on the small-signal input amplitude, and provided that total voltage and current signals (including bias) are considered in the energy balance. Potentially severe incorrect dynamic behaviour can result from the violation of such bounds, as illustrated through a linearized reduced-order model of a low dropout voltage regulator.

### I. INTRODUCTION

Many nonlinear circuit blocks, such as amplifiers or low-dropout voltage regulators, are designed to operate under small-signal conditions at well-defined bias points. In such conditions, linearized small-signal models can safely replace full transistor-level descriptions during system-level verification via numeric simulations. Standard linear Model Order Reduction procedures can be applied to compress such models (while controlling the approximation error), hence enabling drastic reduction in transient simulation runtime. Speedup of up to three orders of magnitude have been reported in [1]–[4].

However, the above numerical simulation flow can be safely adopted only when the amplitude of the small-signal inputs is below a given threshold  $\delta$ , which defines a trust region for accuracy. For larger inputs, the accuracy of the numerical results cannot be guaranteed, mainly due to the linearization error in the small-signal model extraction.

In this work, we consider a second and more subtle limitation arising from energy balance considerations. We show that even if small-signal models behave as locally active (e.g. power amplifiers), they are in fact dissipative when their dynamics are described using total voltages and currents (including bias terms) at all ports (including power supply ports). Such models are henceforth called *affine linearized models*. This is explained by the observation that any circuit block that does not include independent sources is dissipative, since energy is only provided from the external environment through power supply. A locally active behavior arises due to internal energy redistribution from the DC bias to the small-signal components.

Following the theory in [5], we provide a characterization of the energy behavior of affine linearized models. It is shown that dissipativity holds only when the amplitude of the small-

signal input components is bounded by some threshold  $\gamma$ , generally larger than the accuracy threshold  $\delta$ . We refer to this behavior as *Bounded Input Dissipativity (BID)*. For small-signal inputs larger than  $\gamma$ , dissipativity no longer holds. In such case, a linearized model-based simulation may lead to completely wrong results with self-sustained oscillations or exploding signals, due to the ability of the linearized model to provide an indefinite amount of power or energy. Therefore, the qualitative behavior of true transistor-level circuit and its linearized model may be dramatically different when BID does not hold. We illustrate this concept through a simple example of a low dropout voltage regulator, whose linearized model is driven to instability by a small-signal input with an amplitude that violates the limits imposed by proposed BID conditions.

#### II. BACKGROUND: AFFINE LINEARIZED MODELS

Let us consider a generic nonlinear dynamic M-port system, driven by inputs  $u \in \mathbb{R}^M$  with resulting outputs  $y \in \mathbb{R}^M$ . Without loss of generality, we consider a voltage-controlled setting, so that u collects the total port voltages and y the corresponding port currents. We assume normal sign reference at all ports, so that the instantaneous power entering the M-port is  $p(t) = u(t)^\top y(t)$ .

We assume that the circuit block is biased by an external power supply, set at a stable operating point. The corresponding DC values of input and output are denoted as  $U_0$  and  $Y_0$ , respectively. Assuming small-signal operation, we split total voltages and currents as

$$u(t) = U_0 + \tilde{u}(t), \quad y(t) = Y_0 + \tilde{y}(t),$$

(1)

where  $\tilde{u}(t)$  and  $\tilde{y}(t)$  are small-signal components. After a linearization process followed by a model order reduction, one obtains the following behavioral state-space representation

$$\dot{\tilde{x}}(t) = A\,\tilde{x}(t) + B\,\tilde{u}(t), \quad \tilde{x}(0) = 0

\tilde{y}(t) = C\,\tilde{x}(t) + D\,\tilde{u}(t),$$

(2)

where the small-signal states  $\tilde{x}(t)$  are induced by the particular algorithm used to derive the model. In this work, we use for instance a data-driven approach [1] where the circuit block is first characterized through its small-signal AC responses via SPICE runs, which are then subjected to a rational approximation based on Vector Fitting [6] followed by a state-space realization [7]. The small-signal transfer function of (2) is

$$\tilde{H}(s) = D + C(sI - A)^{-1}B.$$

(3)

<sup>&</sup>lt;sup>‡</sup> Dept. Electrical Engineering and Computer Science, Massachusetts Institute of Technology, USA

Model (2) is intended to replace the complete transistorlevel circuit block in numerical simulations. Therefore, not only the small-signal dynamics, but also the DC bias levels must be correctly included. This is possible by augmenting (2) by an affine term in the output equation

$$\dot{x}(t) = Ax(t) + Bu(t), x(0) = X_0$$

$$y(t) = Cx(t) + Du(t) + Y_C,$$

(4)

where

$$Y_C = Y_0 - (CX_0 + DU_0)$$

and  $X_0 = -A^{-1}BU_0$ . (5)

We call (4) the affine linearized model. Unlike system (2), this model operates on total voltages and currents, with the initial condition x(0) defined by the operating point through (5). This is the standard setting employed in all circuit simulation environments, in particular SPICE.

#### III. BOUNDED INPUT DISSIPATIVITY

The total input power flow into model (4) is

$$p(t) = u(t)^{\top} y(t) = (U_0 + \tilde{u}(t))^{\top} (Y_0 + \tilde{y}(t)),$$

(6)

where the DC power component is  $P_0 = U_0^{\top} Y_0$ . For all cases of practical interest  $P_0 > 0$ , so that the model receives DC power from its environment when small-signals are zero.

The pure small-signal model (2) may be locally active, so that the transfer function (3) is *not* Positive Real (this is the case, e.g., for power amplifier circuits). It is then conceivable that the small-signal component of the power is  $\tilde{p}(t) = \tilde{u}(t)^{\top} \tilde{y}(t) < 0$ , as an indication of being locally active. Increasing the amplitude of  $\tilde{u}$  leads to a (quadratic) increase of the small-signal power. Therefore, it is to be expected that the full model (4) based on total signals (DC + small signals) exhibits a transition in behaviour from dissipative when small signals are turned off, to non-dissipative when small-signals exceed an amplitude bound  $\gamma$ . This is precisely the concept of *Bounded Input Dissipativity* that we discuss in this work.

The BID characterization requires a number of technical arguments [5], we recall here only the main points in view of the illustrative example of Sec. IV. Model (4) is *dissipative* according to the classical definition [8] if there exists a storage function of the state  $E(x) \geq 0$  (here assumed differentiable for simplicity) such that for each solution of (4) one has

$$\frac{d}{dt}E(x(t)) \le p(t) \quad \forall t \ge 0. \tag{7}$$

Equivalently, the rate of increase of stored energy cannot exceed the total power received from the environment.

Let us consider the class of one-sided input signals with bounded amplitude and superimposed bias,

$$u(t) = U_0 + \tilde{u}(t), \quad \|\tilde{u}(t)\|_2 \le \gamma \ \forall t, \ \tilde{u}(t) \equiv 0 \ \forall t \le 0.$$

(8)

Subject to such inputs, the states x of (4) are driven by the system dynamics within a region that is usually denoted as reachability set  $R_{\gamma}$ , so that  $x(t) \in R_{\gamma}$  for all  $t \ge 0$ . It can be shown that this set can be expressed as  $R_{\gamma} = X_0 + R_{\gamma}^0$ , where  $R_{\gamma}^0$  is the reachability set of the small-signal model (2) subject

to small-signal inputs  $\tilde{u}$ . To enable further derivations, this set is here overbounded by an ellipsoid  $R_{\gamma}^0 \subseteq \{\tilde{x}: \tilde{x}^{\top}W\tilde{x} \leq \gamma^2\}$ , with matrix  $W \succ 0$  determined below.

In order to check dissipativity when inputs are restricted through (8), it is sufficient to produce a storage function E(x) in the domain  $R_{\gamma}$  and enforce (7). Inspired by the linearity of (4) (see also [5]) we consider as possible candidates, quadratic storage functions

$$E(x) = \frac{1}{2}x^{\top}Px + q^{\top}x \tag{9}$$

where  $P = P^{\top}$  is a symmetric matrix (not necessarily sign definite), and q is a vector. This choice enables a direct and convenient algebraic characterization of BID conditions, generalizing the celebrated Kalman-Yakubovich-Popov (KYP) Lemma [9]–[11]. Our main result is expressed as the following

Theorem 1: [5] The affine linearized system (4) is BID with input amplitude level  $\gamma > 0$ , if a matrix P and a vector q exist such that the following inequality holds

$$\tilde{z}^{\top} \Sigma_0(P) \tilde{z} + 2\theta_0(P, q)^{\top} \tilde{z} + \phi_0 \le 0,$$

$$\forall \tilde{x}, \tilde{u} : \tilde{x}^{\top} W \tilde{x} \le \gamma^2, \, \tilde{u}^{\top} \tilde{u} \le \gamma^2$$

(10)

where

$$\Sigma_{0} = \begin{bmatrix} A^{\top}P + PA & PB - C^{\top} \\ B^{\top}P - C & -D - D^{\top} \end{bmatrix}, \quad \tilde{z} = \begin{bmatrix} \tilde{x} \\ \tilde{u} \end{bmatrix}$$

$$\theta_{0} = \begin{bmatrix} A^{\top}(PX_{0} + q) - C^{\top}U_{0} \\ B^{\top}(PX_{0} + q) - D^{\top}U_{0} - Y_{0} \end{bmatrix},$$

$$\phi_{0} = -2U_{0}^{\top}Y_{0},$$

$$(11)$$

and  $W \succ 0$  is a matrix that obeys the matrix inequality for some scalar  $\alpha \geq 0$ ,

$$\begin{bmatrix} A^{\top}W + WA + \alpha W & WB \\ B^{\top}W & -\alpha I \end{bmatrix} \leq 0.$$

(12)

We remark that setting  $U_0=0$  and q=0 reduces (10) to the standard KYP Lemma, which deals with  $\gamma=\infty$ , i.e. the standard notion of dissipativity for linear systems. The advocated generalization includes additional non-homogeneous terms that represent the DC power contribution (term  $\phi_0$ ) and the coupling between DC and AC powers (term  $\theta_0$ ).

Theorem 1 provides purely algebraic conditions expressed in terms of Linear and Bilinear Matrix Inequalities, whose verification can be performed through dedicated solvers. Three different algorithms are presented and discussed in [5]. In practice, one can first fix a value for  $\gamma$  and then verify whether the conditions in Theorem 1 are feasible for that value. An iterative search on  $\gamma$  can then be performed to find the largest  $\gamma_{\rm max}$  for which BID can be established. When exceeding this amplitude, the system may not behave as dissipative and numerical simulation issues could very easily be expected. An illustrative example follows.

# IV. AN EXAMPLE

We consider a basic system simulation involving a Low Drop-Out (LDO) regulator circuit based on the design presented in [12] and implemented in a 40 nm CMOS process. A

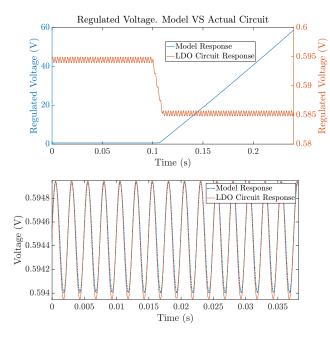

Fig. 1. Transient voltage of the LDO obtained with transistor-level circuit (red) and reduced model (blue). Top panel: model response diverges when Bounded-Input Dissipativity is lost (around  $t=0.1\,\mathrm{s}$ ). Bottom panel: zoomed view for early time.

linearized reduced order model of order 9 was generated from small-signal AC responses of a full layout extraction including parasitics, considering the operating point

$$U_0 = \begin{bmatrix} V_{\mathrm{DD}} \\ -I_{\mathrm{L}} \end{bmatrix} = \begin{bmatrix} 1.1\,\mathrm{V} \\ -1.02\,\mathrm{mA} \end{bmatrix}, \quad Y_0 = \begin{bmatrix} I_{\mathrm{DD}} \\ V_{\mathrm{L}} \end{bmatrix} = \begin{bmatrix} 1\,\mathrm{mA} \\ 0.594\,\mathrm{V} \end{bmatrix},$$

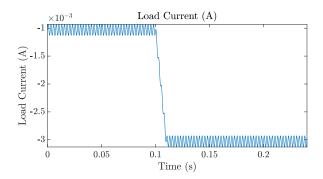

where  $V_{\rm DD}$  is the DC input voltage and  $I_{\rm L}$  is the DC load current. The allowed small-signal bound for model dissipativity,  $\gamma_{\rm max} = 0.062$ , is computed in 3 s. Both model (few kB netlist size) and transistor-level circuit (30 MB netlist size) were used in a system-level transient simulation, that included a diode in combination with an input capacitor in order to prevent possible reverse currents that could damage the regulating device [13]. As the load current fluctuations increase beyond  $\gamma_{\rm max}$ , the model starts to inject energy into its terminations (Fig. 2). This energy flow causes an uncontrolled increase of the input voltage, and consequently, of the regulated voltage at Port 2 (Fig. 1, top panel, blue line). This phenomenon is not observable when the actual transistor-level circuit is employed in the simulation (Fig. 1, top panel, red line), despite the response of the model being extremely accurate with respect to the transistor-level circuit (Fig. 1, bottom panel).

## V. CONCLUSIONS

Linearized models of active circuit blocks can be safely employed in system-level transient simulations only when the amplitude of the small-signal inputs are constrained to a well-defined trust region. Beyond accuracy considerations, we have shown that the concept of Bounded Input Dissipativity and the associated conditions may lead to an a priori determination of the maximum input bound  $\gamma_{\rm max}$  that guarantees a

Fig. 2. Transient load current applied to the LDO. The amplitude of the small-signal current  $\tilde{\imath}_L$  undergoes a jump at  $t=0.1\,\mathrm{s}$  such that its amplitude exceeds the maximum allowed BID bound  $\gamma_{\mathrm{max}}$ .

physically-consistent energy behavior of the linearized models. We suggest that such conditions should be embedded in next-generation circuit and system solvers that employ behavioral reduced-order models of active circuit blocks, in order to provide automated self-consistency checks at runtime. This might avoid running models outside their validity limits, thus preventing designers to draw incorrect conclusions about the behavior of their systems.

#### REFERENCES

- S. B. Olivadese, G. Signorini, S. Grivet-Talocia, and P. Brenner, "Parameterized and DC-compliant small-signal macromodels of RF circuit blocks," *IEEE Trans. Components, Packaging and Manufacturing Technology*, vol. 5, no. 4, pp. 508–522, 2015.

- [2] T. Bradde, P. Toledo, M. De Stefano, A. Zanco, S. Grivet-Talocia, and P. Crovetti, "Enabling fast power integrity transient analysis through parameterized small-signal macromodels," in *International Symposium* on Electromagnetic Compatibility, Barcelona, Spain, 2019, pp. 759–764.

- [3] B. Nouri, M. S. Nakhla, and X. Deng, "Stable model-order reduction of active circuits," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 7, no. 5, pp. 710–719, May 2017.

- [4] B. Nouri and M. S. Nakhla, "Efficient time-domain sensitivity analysis of active networks," *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 9, no. 9, pp. 1721–1729, Sep. 2019.

- [5] T. Bradde, S. Grivet-Talocia, G. C. Calafiore, A. V. Proskurnikov, Z. Mahmood, and L. Daniel, "Bounded input dissipativity of linearized circuit models," *IEEE Trans. Circuits and Systems I*, in press.

- [6] B. Gustavsen and A. Semlyen, "Rational approximation of frequency domain responses by vector fitting," *IEEE Trans. Power Delivery*, vol. 14, no. 3, pp. 1052–1061, 1999.

- [7] S. Grivet-Talocia and B. Gustavsen, Passive Macromodeling: Theory and Applications. John Wiley & Sons, 2015.

- [8] J. C. Willems, "Dissipative dynamical systems part I: General theory," Archive for Rational Mechanics and Analysis, vol. 45, no. 5, pp. 321–351, 1972.

- [9] B. D. O. Anderson and S. Vongpanitlerd, *Network Analysis and Synthesis*. Prentice-Hall, 1973.

- [10] V. Popov, "Absolute stability of nonlinear systems of automatic control," Autom. Remote Control, vol. 22, no. 8, pp. 857–875, 1962.

- [11] V. Yakubovich, "Solution of some matrix inequalities encountered in the nonlinear control theory," in *Dokl. Akad. Nauk SSSR*, vol. 156, no. 2, 1964, pp. 278–281.

- [12] T. Y. Man, P. K. Mok, and M. Chan, "A high slew-rate push-pull output amplifier for low-quiescent current low-dropout regulators with transient-response improvement," *IEEE Trans. Circuits Syst. II: Express Briefs*, vol. 54, no. 9, pp. 755–759, 2007.

- [13] M. Sellers, "LDO basics: Preventing reverse current." [Online]. Available: https://e2e.ti.com/blogs\_/b/powerhouse/archive/2018/07/25/Ido-basics-preventing-reverse-current-in-ldos