# DESIGN OF A PHASE LOCKED LOOP BASED CLOCKING CIRCUIT FOR HIGH SPEED SERIAL LINK APPLICATIONS

#### BY

#### RISHI RATAN

#### THESIS

Submitted in partial fulfillment of the requirements for the degree of Master of Science in Electrical and Computer Engineering in the Graduate College of the University of Illinois at Urbana-Champaign, 2014

Urbana, Illinois

Adviser:

Professor José Schutt-Ainé

# ABSTRACT

Technology scaling and unprecedented growth in demand for ubiquitous, fast, robust computing have been the driving forces leading the innovations in high-speed interfaces. With the rise of heavy duty data centers to handheld mobile devices, the desire for faster, low-power integrated inter-IC communication protocols is at an all-time high and has led the roadmap of the semiconductor industry, making it one of the fastest growing yet fiercely competitive industries. With the growing needs for ultra-low power yet multi-Gbps signaling in both wired as well as wireline applications, integrated systems on chip (SoCs) have become mainstream critical components in modern computing systems. The ability to process and access 'big-data' is the fundamental demand in modern society where every second saved in prompt communication as well as computation of information is critical. In order to meet these needs of fast, robust signaling over the same old "lossy" channels, the clock-frequencies need to scale accordingly and clever I/O links need to be developed. The most crucial component of any high-speed I/O link is the clocking circuitry: clock generator at the transmit (TX) end and clock-recovery unit on the receive (RX) end.

This thesis provides an in-depth tutorial on circuit design, analysis and simulation of on-chip PLL based clocking generator circuits for high-speed serial link applications. An overview of high-speed links, along with the basic building blocks that make up a serial link, is presented. The fundamentals of PLLs are introduced and a complete guide to analysis and simulation of a charge-pump phase-locked loop based clocking circuit at both behavioral as well as transistor levels is presented for use as a synthesizer in a serial link. Finally, a survey of potential future research areas to explore for both PLLs in high-speed links as well as the complete serial link is provided with an emphasis on signal integrity applications for future students pursuing graduate studies in the fields of Signal Integrity and Mixed-Signal IC Design.

To my family and friends, for their love and support.

## ACKNOWLEDGMENTS

As I approach the finishing stages of my graduate career, looking back there are countless individuals who have helped make this journey special and memorable. Graduate school is full of numerous uncertainties, various road-blocks in terms of design and implementation of ideas; thus it is a journey that though embarked on by one individual, really is a culmination of the efforts of many people who have helped behind the scenes along the way. At the end of it all, it is this support system that I am deeply indebted to for helping each step of the way, motivating me in the most difficult of times where there were only questions and no answers.

First and foremost, I want to thank my wonderful advisor Professor José Schutt-Ainé for being my mentor, always motivating me to push myself to the next level and being there for me like family. Dr. Schutt-Ainé was one of the first to see potential in me back when I was just a sophomore and had no direction in what I wanted to pursue in my career. He introduced me to the field of circuits and sparked an interest in engineering. He has always been extremely patient throughout the countless occasions I have visited his office hours. Being a mentor and father-figure for me throughout my educational career at UIUC, Prof. Schutt-Ainé has been the biggest contributor to my successes throughout my collegiate career and will forever be a role-model who I look up to as I start my professional career in industry.

Secondly, I would like to convey my heartfelt thank you to Professor Pavan Kumar Hanumolu for guiding me throughout this thesis as a mentor. Prof. Hanumolu stood by me with patience throughout the course of this thesis work, and took time off from his busy schedule in providing me formal lectures on PLLs one-on-one in his office at a time when it was very hectic for him given that he had just moved to UIUC. Without Dr. Hanumolu's constant guidance and feedback this thesis would never have been completed.

Thirdly, I would like to sincerely thank my wonderful colleagues, mentors

and friends in graduate school: Da Wei, Xu Chen, Tom Comberiate, Romesh Nandwana, Mrunmay Talegaonkar, Yubo Liu, Ahmed Elkholy, Saurabh Saxena, Tejasvi Anand, Guanghua Shu, Woo-Seok Choi, Drew Newell, Xinying Wang, Jerry Yang and Maryam Hajimiri for always being patient to answer all my questions, solving arcane problems during the simulation and design process. These fine graduate students have stood by me since day one, provided constructive criticism on my work, painstakingly critiqued every figure and most importantly constantly pushed me towards striving for nothing short of excellence.

Furthermore, I am extremely grateful to Professor Steven Franke, Professor Christopher Schmitz, Professor Milton Feng, Professor Elyse Rosenbaum, Professor Naresh Shanbhag, Professor Venugopal Veeravalli and Dr. Chandrashekhar Radhakrishnan for supporting me throughout my educational career at UIUC and mentoring me every step of the way. Even when the chips were down, they always believed in me and helped me gain an opportunity to pursue my graduate studies.

I thank my family for always being by my side, motivating me to move forward whenever I was faced with roadblocks. Lastly, I am eternally grateful to my friends Ian Wetherbee, Rohan Bambery, Eric Iverson, Pourya Assem, Sai Zhang, Min-Sun Keel, Anish Chivukula, Eclair Hanjing Gao, Dennis Yuan, Jerry Sun, Nishant Nookala and Eric Kim for always standing by me throughout my ECE career at UIUC. I am positive I have missed a few people from the above list but I truly am very thankful to all those who I have interacted with throughout my time at UIUC. Additionally, I am very grateful for getting an opportunity to work with wonderful undergraduates Rushabh Mehta, Ishita Bisht, Brady Salz, Ankit Jain, Haodong Guo, and Pradyut Paul who have worked very diligently in getting the High Speed-SerDes Design project off the ground from scratch.

# TABLE OF CONTENTS

| CHAPT | TER 1 INTRODUCTION                               | 1  |

|-------|--------------------------------------------------|----|

| 1.1   | Motivation                                       | 1  |

| 1.2   | Outline                                          | 3  |

| CHAPT | ΓER 2 HIGH SPEED SERIAL LINKS OVERVIEW           | 5  |

| 2.1   | Simple Link Design                               | 5  |

| 2.2   | Serial vs. Parallel Data Transmission            | 7  |

| 2.3   | SerDes Building Blocks                           | 8  |

| CHAPT | ΓER 3 PLL THEORY AND BACKGROUND                  | 17 |

| 3.1   | PLL Applications                                 | 17 |

| 3.2   | Basic PLL Building Blocks                        | 17 |

| CHAPT | ΓER 4 PLLs IN CLOCKING CIRCUITS                  | 23 |

| 4.1   | Charge-Pump (CP) PLLs Overview                   | 23 |

| 4.2   | CPLL Linear Model and Analysis                   | 24 |

| 4.3   | CPLL Noise-Analysis                              | 26 |

| CHAPT | ΓER 5 PLL BASED CLOCK GENERATOR                  | 29 |

| 5.1   | PFD                                              | 29 |

| 5.2   | CPs                                              | 31 |

| 5.3   | LF                                               | 32 |

| 5.4   | VCOs                                             | 33 |

| 5.5   | Divider                                          | 34 |

| CHAPT |                                                  | 35 |

| 6.1   | Why Behavioral Modeling?                         | 35 |

| 6.2   | Why Verilog-AMS?                                 | 35 |

| 6.3   | Basic Verilog-A/AMS Syntax                       | 36 |

| 6.4   | PLL Simulation in AMS Using Cadence Virtuoso     | 38 |

| CHAPT | ΓER 7 TRANSISTOR LEVEL SIMULATION                | 54 |

| 7.1   | What is SPICE?                                   | 54 |

| 7.2   | SPICE vs. Spectre                                | 54 |

| 7.3   | Transient, PSS and PNoise Simulation Overview    | 55 |

| 7.4   | PLL Simulation in Spectre Using Cadence Virtuoso | 56 |

|       | TER 8 DISCUSSION                                  |

|-------|---------------------------------------------------|

| 8.1   | Conclusion                                        |

| 8.2   | Future Work                                       |

|       |                                                   |

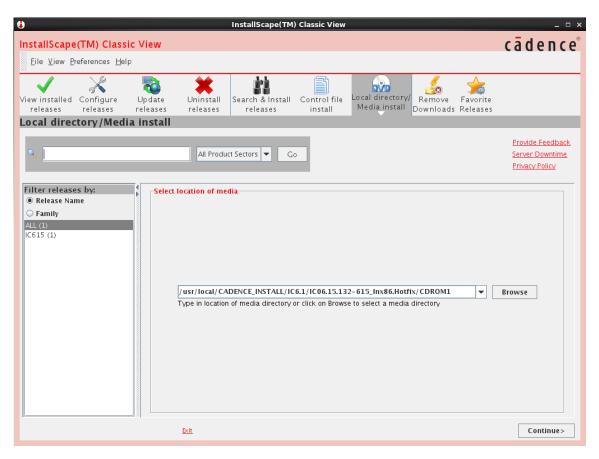

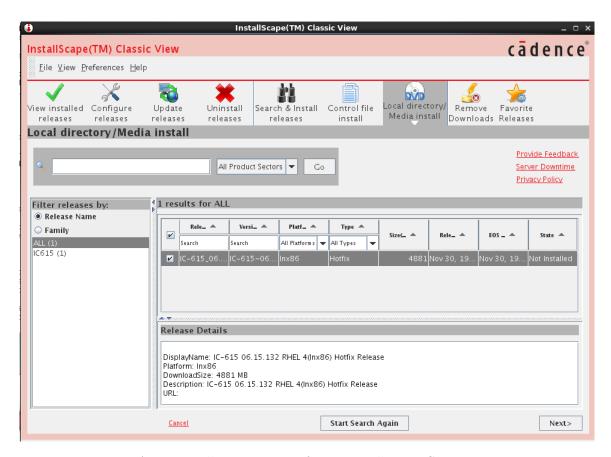

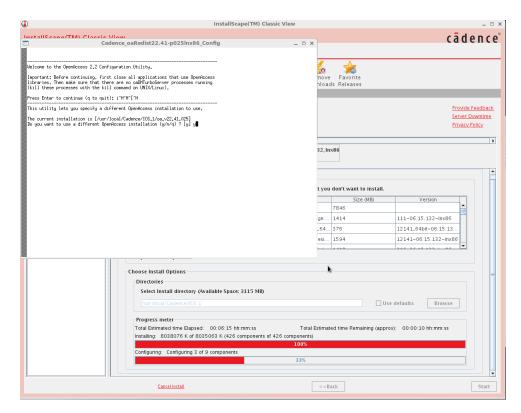

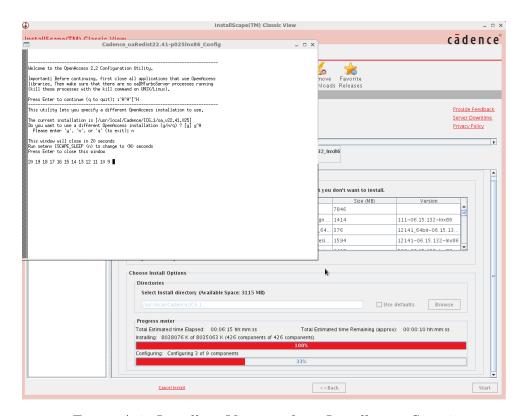

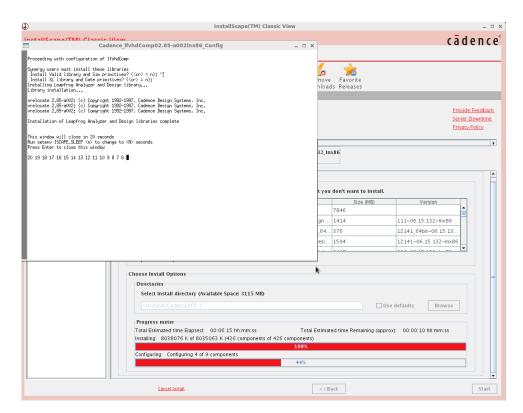

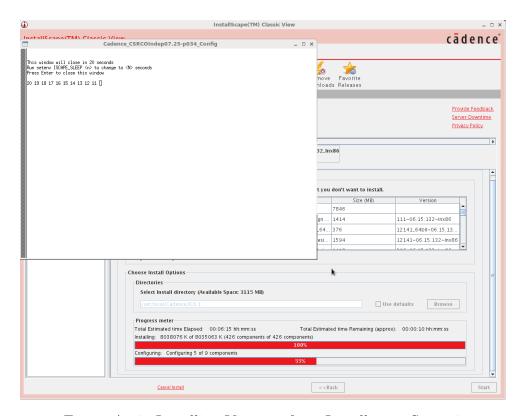

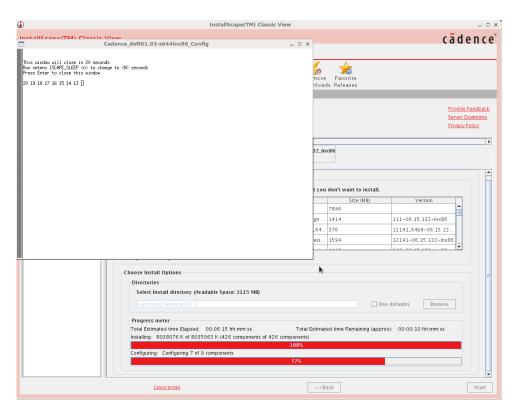

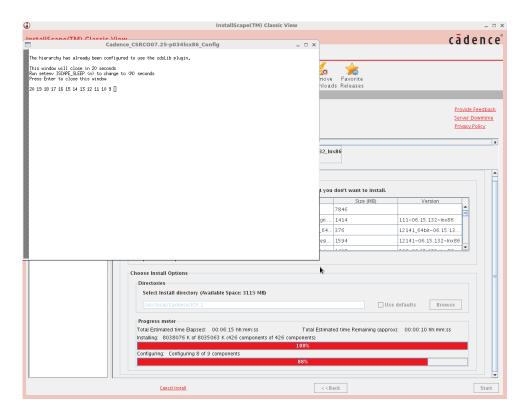

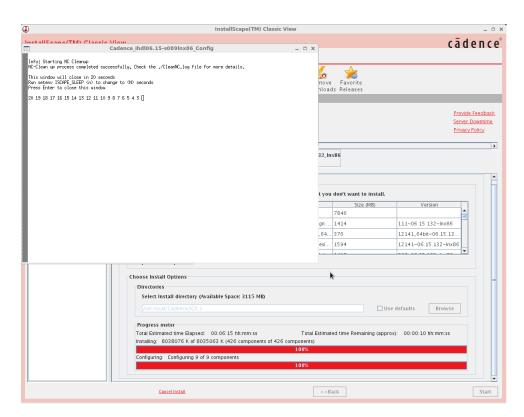

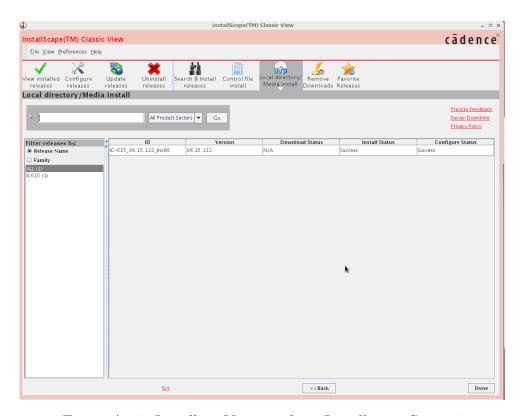

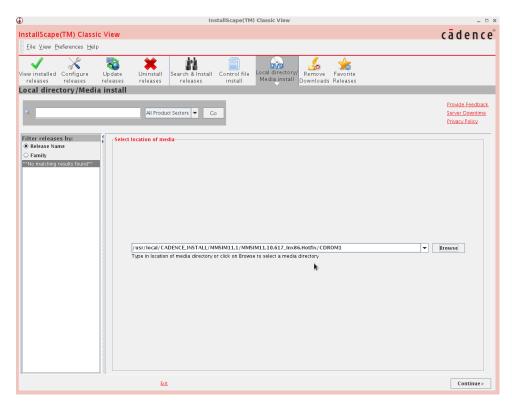

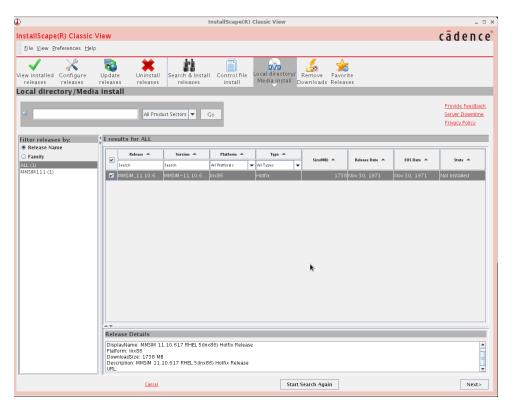

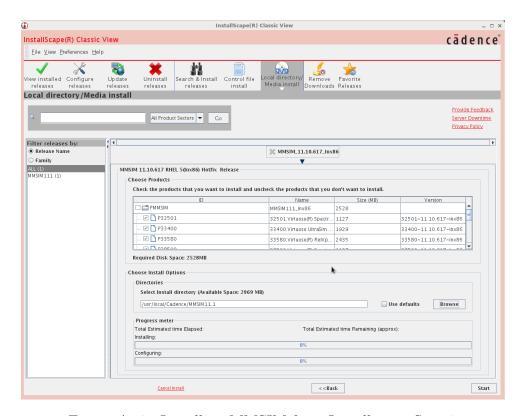

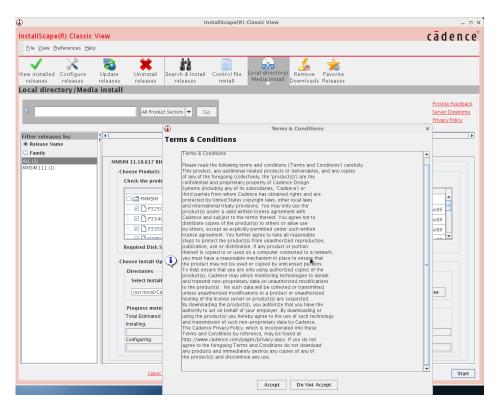

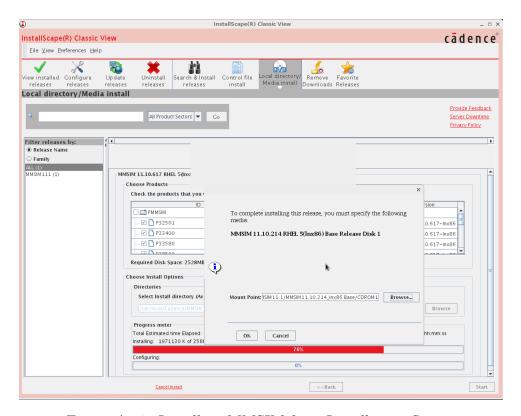

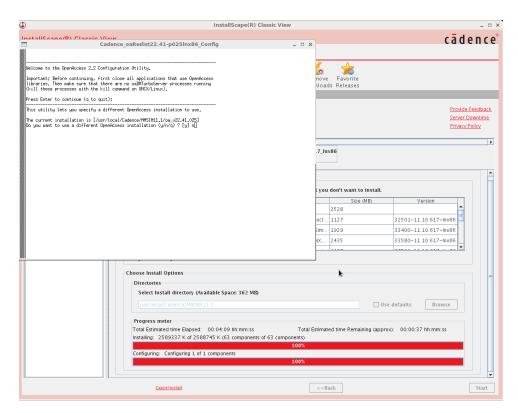

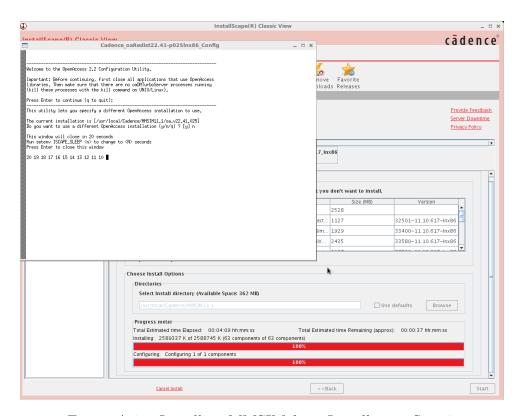

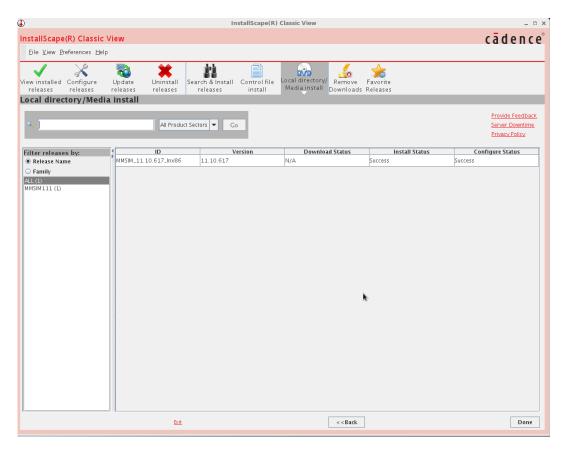

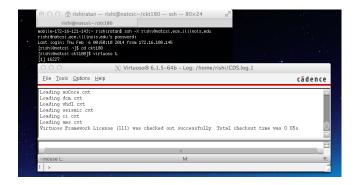

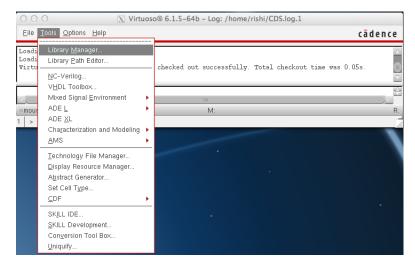

| APPEN | IDIX A   CADENCE VIRTUOSO INSTALLATION GUIDE   92 |

| A.1   | Introduction                                      |

| A.2   | Environment Setup                                 |

| A.3   | Common Troubleshooting Tips                       |

|       |                                                   |

| REFER | ENCES                                             |

# CHAPTER 1

# INTRODUCTION

#### 1.1 Motivation

Over the last 50 years, advances in Semiconductor Fabrication Technology (SFT) coupled with innovations in Integrated Circuit (IC) technology scaling have fueled an unparalleled growth in computing. This aggressive scaling has revolutionized every aspect of modern society and triggered an insatiable demand for faster data rates and higher processing power resulting in clock frequencies and corresponding data rates approaching multi-GHz and multi-Gbps ranges in everyday computing devices like personal computers, mobile devices, entertainment consoles and other such devices. Access to information promptly and efficiently in terms of power and portability/ease of use is the major driver pushing the limits of IC technology. Thus, the need for robust, high-speed, low-power and highly integrable compact systemson-chip (SOCs) is paramount for inter-IC communication interfaces such as network switches, processor/memory interfaces across backplane channels. In order to meet this growing demand for wideband systems, the Input/Output (I/O) links need to scale proportionally with the increased data-rate scaling; however in reality the off-chip I/O bandwidth (BW) has not scaled appropriately and has become a major bottleneck in the overall system performance. Furthermore, along with the off-chip I/O BW limitations, the channel as well as package/connector interfaces have not scaled with SFT making the design of high-speed I/O links extremely challenging due to the increased transmission line loss, crosstalk, and signal distortion resulting in intersymbol interference. As the demand for high data-rate interfaces has skyrocketed, the clock-frequencies needed to realize such systems have correspondingly reached the multi-GHz range necessitating the use of phase-locked loops (PLLs) for on-chip clock synthesis.

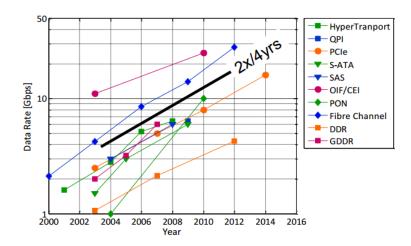

Figure 1.1: IO Link Signaling Data-Rate Trends

Figure 1.1 shows the trends in data-rate scaling of I/O high-speed signaling links as forecasted by the International Solid State Circuits Conference (ISSCC) 2011 annual semiconductor roadmapping report [5]. The key takeaway from this graph is that the data-rates in inter-IC communication links are scaling by a factor of 2X every 4 calendar years while IO channel BW remains the same. The I/O BW scaling problem aside, the ability to design robust, low-jitter on-chip clock synthesizer circuits is in itself an extremely challenging task. Though research in the field of integrated high-frequency clocking circuits has been going on for the past two-decades and lots of innovative designs have come into existence, one common facet missing from the whole paradigm is complete documentation on process of simulation using the Electronic Design Automation (EDA) tools [6]. Most of the literary works in this area primarily focus on novel system level designs for PLL based clock synthesizers and some go into transistor-level details of the sub-blocks; however very rarely do any of the prominent works describe the actual simulation process. As the clock-frequencies scale and demand for robustness in the on-chip synthesizers increases, circuit designers also need to be aware of potential Signal-Integrity (SI) problems associated with their intricate designs. Since the channel BW is essentially the same at high-frequencies of operation the PCB traces act as transmission-lines (TLs) leading to severe degradation in signal quality due to reflections, ringing and cross-talk effects. Thus, every integrated circuit designer will invariably face SI problems in their design which until recently was not a concern as the frequencies were low enough that digital design did not require a formal understanding of signal integrity during the development as well as verification process. Therefore, the motivation for this thesis is to bridge the gap between circuit design and simulation for signal-integrity engineers who need the basic expertise in mixed-signal design process to be able to provide the required assistance to IC designers on designing high-speed SI aware systems.

#### 1.2 Outline

This thesis is organized to serve as a training manual for students pursuing mixed-signal integrated circuit design as their field of study in graduate school. The goal is for this thesis to be their go-to guide to grasp a high-level understanding of high-speed links and learn the simulation setup/procedure to validate PLL based clocking circuits using the popular EDA tool Cadence Virtuoso.

- 1. Chapter 1 provides an introduction to the research problem describing the need for high-speed serial links and their future trends.

- 2. Chapter 2 provides an overview of high-speed links with an emphasis on describing each of the building blocks, figures of merit to characterize these links and lay the motivation for the industry-wide shift from parallel to serial-link design for low power, cost-effective robust I/O link design.

- 3. Chapter 3 describes the fundamentals of Phase-Locked Loops (PLLs) and provides a brief overview of their ubiquitous use in modern day wireline/wireless systems.

- 4. Chapter 4 covers a special class of PLLs, Charge-Pump PLLs, and provides a linear model for small-signal as well as noise-analysis of these PLLs.

- 5. Chapter 5 presents the transistor-level design of a Charge-Pump based Integer-N clock generator circuit operating at an output frequency of 1.6GHz.

- 6. Chapter 6 describes the procedure for behavioral modeling and simulation using Verilog-AMS for the clock-generator circuit described in Chapter 5.

- 7. Chapter 7 describes the procedure for transistor-level simulation for the clock-generator circuit described in Chapter 5.

- 8. Chapter 8 concludes the thesis with a discussion of the take-aways from the clocking circuit designed earlier and provides a brief anecdote on the signal integrity focus areas in high-speed link design and lists design improvements on the basic Integer-N analog clock generating circuit to accommodate industry trends within the field.

- 9. Lastly, the Appendix provides a step-by-step guide for installing and configuring the Cadence Virtuoso environment.

# CHAPTER 2

# HIGH SPEED SERIAL LINKS OVERVIEW

### 2.1 Simple Link Design

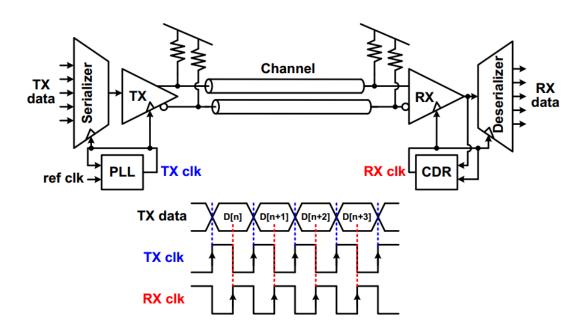

Figure 2.1: Typical High-Speed Link Block Diagram

Generalized model of a High-Speed Serial Link (HSSL), as shown in Figure 2.1 [1], consists of a serializer and transmitter (TX) driven by a PLL clock synthesizer, a channel and a receiver (RX) and Deserializer driven by a Clock-Data Recovery (CDR) unit. The serializer accepts the incoming parallel data-stream and converts it into a serial data-stream which is then sent to the transmitter. The TX generates a train of pulses depending on the data symbols to be transmitted across the channel and the pulse-width which is determined by the timing instant of the transmit clock at both begin/end/edges. The receiver basically comprises a sampler and a decision

circuit whose purpose is to sample the received data-bit stream from the channel and recover, both the transmitted data as well as the clock. Once the receiver recovers the transmitted serial bit-stream it is sent to the Deserializer block whose job as the name suggests is to convert the received serial data back to its original parallel form for future interfaces.

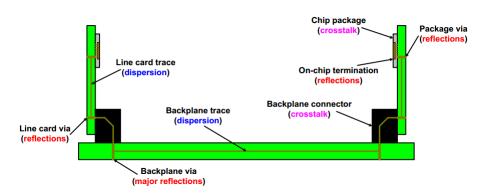

Figure 2.2: Typical Backplane Channel Interface

As discussed in the previous chapter, though the desired data-rates have scaled along with technology scaling, the off-chip channel I/O BW has remained the same. The channel is the electrical path between the TX and RX blocks and in inter-IC communication systems typically comprises printed circuit-board (PCB) traces, vias, connectors and other such I/O interface components. Generally speaking, in high-speed I/O interfaces the channel is typically a 'backplane' which essentially connects two PCBs together and typically looks like the interface shown in Figure 2.2 [1]. The channel is something that the designer has no control over and is thus just a 'known unknown' to the link designer. It is known in the sense that the channel impulse-response is known via measurement of S-parameters of the interface using a Vector-Network-Analyzer (VNA) or via computational electromagnetic modeling software such as Ansys HFSS. The manner in which channel degrades the transmitted signal stream is the unknown aspect and the designer's aim is to design a mechanism for counteracting this degradation. Thus, the whole challenge in high-speed link design is that we need to design a high signal-fidelity communication system that is fast, robust to losses incurred in the channel and on top of all this it needs to be low-power and must occupy the least possible area. The challenge in meeting all of the aforementioned requirements is that at high-speeds the channel suffers from various kinds of microwave losses due to impedance discontinuities between connectors, substrate loss, cross-talk effects, reflections and ringing, all which are difficult to predict and model [1].

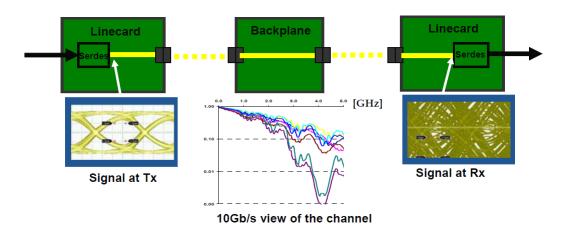

Figure 2.3 [2] shows an example of the I/O link interface for a 10Gbps serial link across a backplane channel. Notice that a clean signal when transmitted across a backplane channel incurs tremendous amounts of loss from the channel at an operating speed of 10Gbps making the signal at the receiver virtually indistinguishable from noise and thus virtually garbage. In order to limit the degradation of signal quality during transmission and reception, the goal of mixed-signal designers is to design fast high-frequency clocks with minimum timing skew at the TX end and minimal sampling errors at the RX end.

Figure 2.3: 10Gbps Backplane Serial Link Interface

#### 2.2 Serial vs. Parallel Data Transmission

Historically, parallel links have been widely used in I/O systems that are connected to the CPU in computers via interfaces like PCI, PCI-X buses. However, as the data-rates have scaled into multi-gigabit ranges, the parallel link performance has not scaled accordingly with high signal fidelity. The tolerance level in timing skew between parallel signaling links has reached the practical limit achievable using traditional printed-circuit-boards (PCBs) that typically use FR-4 substrates. Additionally, as the supply voltage levels in modern CMOS process technologies have scaled down tremendously, the legacy parallel bus voltage levels have not scaled proportionally, making

them incompatible with modern processes [6]. Thus, in order to mitigate this performance limitation and supply voltage scaling problems posed by conventional parallel-link design the industry has shifted to electrical point-to-point serial link interfaces.

Serial links occupy small area on chip and require very few I/O pins as compared to case of parallel links because the number of pins is not directly proportional to the number of data input/output signals. In serial communication links clock-skew is not a problem at the receiver since TX clock is typically not forwarded to the RX. In parallel links, on the other hand clock-skew is the major source of signal degradation at the RX side since the TX clock and data are transmitted separately. Furthermore, cross-talk effects are minimized in serial links due to the absence of multiple conducting channels in parallel that each have varying signals transmitted, whereas in parallel links this is a major problem due to the presence of capacitive/inductive coupling between multiple conducting parallel interconnect channels.

In the consumer electronics industry, serial links have found widespread acceptance in the form of USB (Universal Serial Bus) that connects peripheral electronic systems to computer, and SATA (Serial Advanced Technology Attachment) which connects the computer motherboard with mass storage devices (e.g. hard disk) and PCI-Express (Peripheral Component Interconnect) that is used to connect cards (sound, video or other) to the motherboard. Therefore serial communication has become the solution to higher and more efficient data transmission in order to meet the demands and trends of the higher capacity of communication technology [7].

### 2.3 SerDes Building Blocks

#### 2.3.1 Serializer

The serializer circuit, as the name suggests, converts the input parallel-bus data into a serial bit-stream form. It is a completely digital block and it precedes the TX driver circuit. At a fundamental level, a serializer is essentially a Multiplexer circuit whose driving clock for the serialization process is the TX\_CLK signal generated by the TX PLL.

#### 2.3.2 Driver Amplifier

Driver amplifiers are found both at the TX as well as RX ends. The DA (Driver Amplifier) is used to amplify the input serial bit-stream before it is sent to the receiver through the channel. Another important task accomplished by the DA is that it provides impedance terminations that terminate the channel input/output with  $50\Omega$  impedance.

#### 2.3.3 Phase-Locked Loop (PLL) Clock Generator

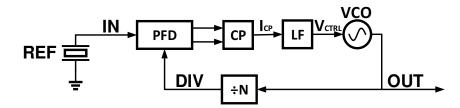

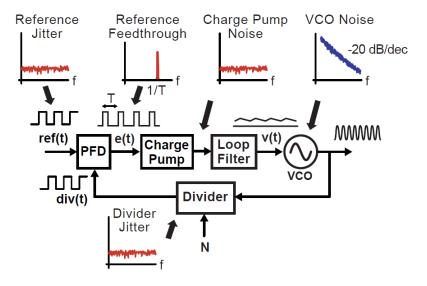

Figure 2.4: Typical PLL Based Clock-Generator Block Diagram

A PLL is a negative feedback system whose sole purpose is to use a reference input clock of frequency  $f_{REF}$  and generate a local clock on-chip at a desired frequency,  $f_{OUT}$ , such that the output clock is matched in phase to the input clock and  $f_{OUT} = \alpha f_{REF}$ , where  $\alpha$  is a multiplying factor. PLLs are used in every modern day high-speed system whether it be wired or wireless because generating a high spectral purity clock at microwave frequencies/data-rates is practically not feasible yet. Piezo-electric crystals are used exclusively as the reference clocks for almost every on-chip interface system because they have the highest-spectral purity and can output truly periodic, jitterfree clock signals typically up to 200MHz. Due to the insatiable demand for robust, high-speed signaling, a mere crystal oscillator is not enough to meet the necessary requirements, so a PLL is essential. The most important task of a PLL is therefore to produce clock signals with minimal timing noise, i.e. the lowest possible jitter (in time domain) and phase-noise (in frequency-domain). At a block-level, a typical PLL clock-generator circuit (as shown in Figure 2.4) used to generate the high-speed on-chip clocks consists of a phase-frequency detector (PFD), charge-pump (CP), loop-filter (LF), voltage-controlled oscillator (VCO) and clock-divider (DIV). PFD tracks the phase and frequency difference between the reference signal and the divider

output signal outputs digital pulse-width modulated (PWM) signals to the CP which essentially converts these digital pulses into an analog current signal. The LF then takes the CP output current signal, low-pass filters the high-frequency noise components and outputs a control voltage that drives the VCO. The VCO is the most-critical component within the PLL as it is the circuit-block that generates the final output clock that is used to drive the digital circuits of the link. Thus, a low phase-noise VCO is of paramount importance in the PLL as the VCO phase-noise is the dominant noise-form in the PLL. Finally, the divider is used in the feedback loop back to the PFD as the VCO output needs to be brought back down to the same frequency level as the reference clock so that the loop can dynamically drive all static-phase errors between reference clock and divider clock to zero such that  $f_{OUT} = \alpha f_{REF}$ , where  $\alpha$  is the multiplying factor and the loop is "locked" to output a stable clock at the desired frequency of operation. The various intricacies involved in PLL design are covered in the remainder of the thesis.

#### 2.3.4 Channel

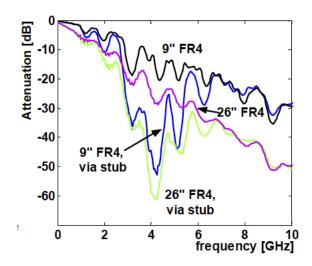

Figure 2.5: Typical Serial Link Channel Responses

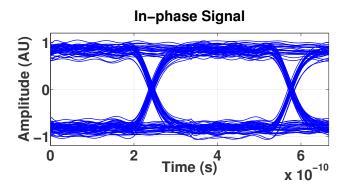

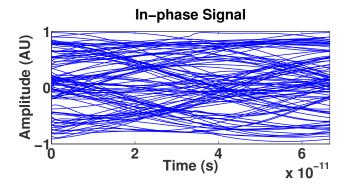

Figure 2.5 [3] shows the attenuation levels a typical serial link channel incurs as a function of operating frequency. Figure 2.6 and 2.7 show the eye diagram outputs from a backplane channel interface at 1Gbps and 10Gbps data-rates respectively. Notice that the eye is fully open at 1Gbps but at 10Gbps the signal is almost indistinguishable from the noise at the receiver side due to

the tremendous loss and distortion incurred along the channel. The HSSL designers need to be able to account for such losses when designing the blocks of the HSSL at both a system as well as circuit level. As stated earlier, the channel induced degradation is the primary limiting factor during the entire link-design process.

Figure 2.6: 1Gbps Backplane Link Eye Diagram

Figure 2.7: 10Gbps Backplane Link Eye Diagram

#### 2.3.5 Equalization

Equalization is a method of combatting the detrimental effects of intersymbol interference (ISI) caused by the bandlimited channel. Equalizers are typically implemented as linear or non-linear adaptive filters. Equalization performed before the channel is referred to as pre-emphasis and basically involves passing the TX signal through a filter whose transfer function is the inverse of the channel transfer function. Conversely, equalization at the RX end is used to undo the distortion incurred in the received signal due to the channel loss and dispersion. Most RX equalization schemes are adaptive and

are implemented using DSP techniques to cancel out the channel loss from the received data-bits.

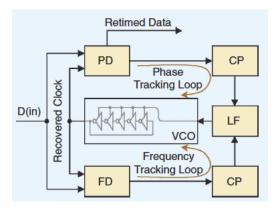

#### 2.3.6 Clock and Data Recovery (CDR)

A CDR as the name suggests is responsible for extracting the clock information of the transmitter from the received signal. In modern HSSLs, a clock-recovery mechanism is essential at the receiver end because TX clock information is typically embedded inside the incoming data pulse-stream at the receiver input. At heart, a CDR is essentially a modified PLL circuit wherein the phase-detector now has to sample the incoming data-stream and extract both data and phase information from it [3]. The PD of the CDR detects the transitions in the received data-stream and the VCO generates a periodic clock that drives the decision circuit within the PD to retime the distorted received data and then regenerates the system clock with lower skew and jitter. CDR design is a lot more intricate than PLL design because in the case of the CDR, loop bandwidth is often very small and governed by the jitter tolerance specifications of the system, meaning there is not much room for VCO phase-noise reduction. The most common implementation of a CDR (as shown in Figure 2.8) includes a regular PLL loop to track the exactfrequency of the TX clock, a phase-tracking loop with special phase-detector to produce the retimed data and a common VCO to output a low-jitter, phase-noise replica of the TX clock.

Figure 2.8: Typical Clock and Data Recovery Unit Implementation

#### 2.3.7 Deserializer

The descrializer circuit, as the name suggests, converts the input serial bitstream data back into its original parallel bus form. It is also a completely digital block and it succeeds the RX driver circuit. Basically, the descrializer is just a demultiplexer circuit that is driven by the clock that is recovered by the CDR.

### 2.3.8 Coding Schemes

Nonreturn-to-zero (NRZ) pulses are commonly used as the basis function for discrete data transmission. The response of the channel to the NRZ pulse is defined as the pulse response and is traditionally used to analyze and model the effects of a channel on data transmission and also in the design of equalizers in the case of channels with large attenuation at the frequency of interest. Apart from NRZ signaling, designers can also implement advanced modulation techniques for faster, robust signaling. For example, multilevel PAM like PAM-4 has much higher spectral efficiencies and can transmit two bits per symbol. This enables the transmission of an equivalent amount of data in half the channel bandwidth. In modern serial links along with the signaling schemes, some amount of encoding is also present in the datastream. Most commonly used encoding schemes are 8B/10B and 16B/20B wherein 10bits or 20bits are sent but only 8bits/16bits are actual meaningful data bits, and this is powerful as it improves the BER. The only drawback of encoding is that it further adds complexity to the transceiver design as a encoder/decoder circuit needs to be designed and more bits need to be sent through the same bandwidth-limited channel.

### 2.3.9 HSSL Figures of Merit

HSSL performance is limited by the channel as well as the process technology used during circuit design. Since data-rates are scaling faster than the available channel bandwidths, the major constraint in realizing robust, high-speed interfaces is improving the maximum available clock frequency for on-chip synthesis. The channel bandwidth is the major constraint in overall system performance; thus, dealing with channel loss and designing clever equaliza-

tion techniques are the biggest design challenges in HSSLs today. Robustness therefore is the most important metric of performance for link designers. The primary figures-of-merit (FOM) for HSSLs are bit-error-rate (BER), jitter, crosstalk analysis and timing/noise analysis [1].

BER in modern HSSLs is typically between  $10^{-12}$  and  $10^{-15}$  and it is the main metric used to signify the integrity of the received data-bits. A BER of  $10^{-12}$  means that 1 bit will incur an error along the link when we transmit a total of  $10^{12}$  bits. Measurement/Estimation of BER is one of the fundamental challenges faced by link designers because in order to accurately conclude that the link actually has a BER of the order  $10^{-12}$ , one needs to simulate a random sequence of at least  $10^{12}$  bits which even in current state-of-the art simulators is next to impossible. Therefore, most simulators use statistical means to collectively analyze the effects of deterministic noise sources such as Intersymbol Interference (ISI), supply-noise, timing-jitter as well as random noise sources like white-thermal noise and random jitter when estimating the system BER.

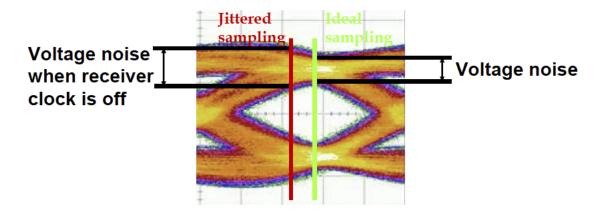

A common method to measure timing jitter is to use eye-diagrams. Eye diagrams are constructed by slicing the time-domain signal waveform into small sections and overlaying them on top of each other such that the resulting shape resembles an 'eye'. The horizontal axis of the eye diagram represents time and is typically one or two symbols wide, and the vertical axis represents the amplitude of the signal. Ideally, we want the eye to be as "open" as possible, since a larger eye opening signifies that there is a large enough margin to meet any voltage and timing requirements needed by the system. Quantitatively speaking, the minimum height and width of the data at the receiver are key metrics for evaluating link performance. As link designers, we want the receiver eye to be wide enough to provide adequate time to satisfy the setup and hold requirement of the flip-flops used, and have sufficient height to ensure that the voltage levels meet  $v_{il}$  and  $v_{ih}$  requirements of the system in the presence of multiple noise sources. Figure 2.9 [6] shows an example of what sampling an eye with and without jitter means.

Figure 2.9: Eye Diagram Terminology and FOMs

The most prominent source of signal degradation in HSSLs over a bandlimited channel is Intersymbol Interference (ISI). ISI results when a sequence of signals are passed through a channel whose bandwidth is insufficient to allow passage of all the spectral components of the signal. It is a form of signal distortion caused due to reflections, channel resonances, and channel loss/dispersion. Simplest way to understand ISI is to view it as interference between symbols wherein current bit/symbol causes distortion in subsequent/preceding bit/symbol. ISI degrades as data-rates increase and channel bandwidth remains the same, and the only way to combat it is through clever equalization techniques on either the TX, RX ends or both. Another form of interference which is slowly becoming a major hindrance for link designers as data-rates scale is crosstalk (XT), which is a phenomenon occurring due to presence of capacitive as well as inductive coupling between neighboring signal lines in a transceiver. Typically, most of the XT effects are felt at the connector/package levels of a channel where the signal spacings are small compared to the distance between shields [6]. Near-End XT (NEXT) and Far-End XT (FEXT) are the two classes of XT wherein NEXT is defined as the XT due to energy dissipated from coupling between transmitted signal and the reflected signal on the same chip, while FEXT is defined as the XT due to energy dissipated from coupling between transmitted signals of two different chips. NEXT is by far the most deleterious type of XT and the most commonly observed kind because the TX energy levels are typically very high compared to the RX signal levels so the received signal can really be submerged inside it if proper care is not taken.

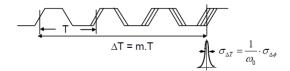

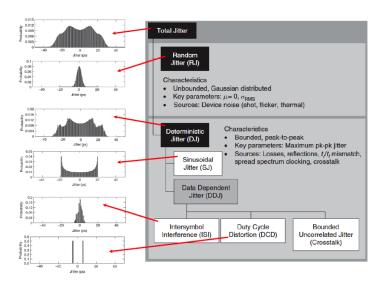

Finally, the last major metric in calculating the timing margin of a HSSL is the jitter. Characterization of deterministic as well as random timing jitter in a clock output is very important to a link designer. Essentially, jitter is the time-domain variation in the clock-signal as shown in Figure 2.10 [10]. A commonly used method for jitter calculation is to close either side of the eye horizontally by the amount of peak clock jitter. While this method can be helpful in evaluating the effects of jitter at the receiver end, we will show in this paper that this is an overly optimistic approximation of noise margin degradation for transmitter jitter. Due to the need for integration of clock generators such as PLLs in large digital chips, clock jitter is dominated by power-supply and substrate noise, both of which do not scale with technology. Therefore, as data rates increase, bit-periods become shorter and the performance of multi-gigabit links will be limited by the clock jitter, thereby initiating the importance of accurately analyzing the effects of clock jitter on high-speed serial links. Figure 2.11 [5] provides a summary of common jitter profiles in a typical serial link.

Figure 2.10: Timing Jitter Example

Figure 2.11: Summary of Common Jitter Profiles

## CHAPTER 3

## PLL THEORY AND BACKGROUND

## 3.1 PLL Applications

Phase-Locked Loops (PLLs) are one of the most fundamental and ubiquitous circuits found in any communications (wireless, wireline) and high-speed digital systems. Monolithic CMOS implementation of PLLs has gained lots of popularity over the last few decades due to an insatiable demand for high performance digital systems. Most common uses of a PLL are in the form of frequency synthesizers and carrier/clock recovery circuits both in the RF domain as well as the high-speed digital domain.

### 3.2 Basic PLL Building Blocks

### 3.2.1 Phase/Phase-Frequency Detector (PD or PFD)

In a PLL, unlike many other feedback systems, the variable of interest changes dimension around the loop: it is converted from phase to voltage (or current) by the phase detector, processed by the LPF as such, and converted back to phase by the VCO. In the lock condition, the input and output frequencies are exactly equal, regardless of the magnitude of the loop gain (although the phase error may not be zero). This is an extremely important property because many applications are intolerant or even small (systematic) differences between the input and output frequencies [15].

The PD compares the phase of the output signal with the phase of the reference signal and develops an output signal that is approximately proportional to the phase-error  $\Phi_e$ . The output voltage of the PD is proportional to the phase-difference between the reference signal and the output signal. The

PD serves as an "error'-amplifier" in the feedback loop, thereby minimizing the phase-difference,  $\Delta \phi$ , between the reference signal,  $V_{ref}(t)$  and the oscillator output signal,  $V_{out}$ . The loop is considered to be "locked" if  $\Delta \phi$  is constant with time, a result of which is that the input and output frequencies are equal. In locked condition, all the signals in the loop have reached steady state and the PLL operates as follows. The phase detector produces an output whose DC value is proportional to  $\Delta \phi$ . The low-pass filter suppresses high-frequency components in the PD output, allowing the DC value to control the VCO frequency. The VCO then oscillates at a frequency equal to the input frequency and with a phase-difference equal to  $\Delta \phi$ . Thus, the LPF filter generates the proper control voltage for the VCO. The VCO phase can be seen to be an initial condition of the system, as it is independent of the initial conditions in the LPF. Whenever two frequencies become equal at a point in time and  $\Delta \phi$  has not established the required control voltage for the VCO, the loop will continue the transient, temporarily making the frequencies unequal again. In other words, both "frequency-acquisition" and "phase-acquisition" must be completed. This behavior is to be expected because for lock to occur again, all the initial conditions of the system, including the VCO output phase, must be updated [15].

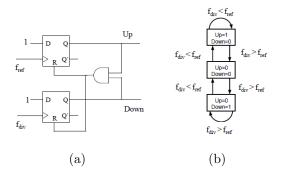

The biggest pitfall of using just a PD is that it does not capture any step changes in frequency; thus, in order to be able to track both phase and frequency we need to use a phase-frequency detector (PFD). The purpose of a PFD is to compare the reference clock signal and the VCO output clock after division in both phase and frequency. These frequencies are generally denoted by  $F_{REF}$  and  $F_{VCO}$  respectively. The basic structure can be divided into logic control part and a charge pump. The charge pump is a current source in series with a current sink and the output node is like a switch that resides in between the source and sink. The logic part consists of two D-Flip-Flops (DFFs) and the outputs of these DFFs control the switch of the charge pump. Conceptually the PFD can be viewed as a state machine with three states. The initial state is 0 and both DFFs will be reset if VCO and reference signal are both high. In state -1 only current sink is turned on and sinks charge out of the load, thereby decreasing the output voltage; in state 0 current source and current sink are turned off so no charge is injected or extracted out of the output node, thereby keeping the output voltage unchanged. In state 1 only current source is turned on so charge can

be injected into the output node, thereby increasing the output voltage. The state transitions are controlled by the edges of VCOs output and reference signal; thus it is clear that the PFD is a purely digital circuit.

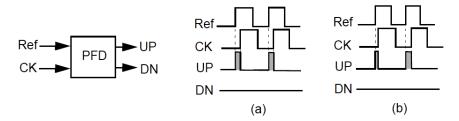

Figure 3.1: PFD Operation

Figure 3.2: PFD Functionality

Figures 3.1 and 3.2 show the block diagram of a PFD and demonstrate its functionality. Essentially, when the reference clock is faster than the divider clock, UP signal is High, DN signal is Low and vice versa. Note that when both the reference and divider clocks are synchronized both UP and DN signals are set to be High. The phase frequency detector (PFD) is a circuit that linearly translates the phase difference into voltage signals. The ideal average input/output relationship should be:

$$V_e = K_{PD} \times \phi_e \tag{3.1}$$

$$where |\phi_e| < 2\pi$$

$K_{PFD}$  is defined as the PFD gain.

#### 3.2.2 Charge-Pump (CP)

The charge pump is the device that translates the digital voltage signals generated from PFD into a current signal. Since the voltage controlled oscillator needs a stable voltage to control the oscillating frequency, a charge storage capacitor is needed. In order dump enough charge into the capacitor, a charge pump is needed here. Together with the PFD the s-domain transform becomes the following:

$$K_{PFD} = \frac{i_{Charge\ Pump}}{2\pi} \tag{3.2}$$

#### 3.2.3 Loop-Filter (LF)

PLLs act as high-pass filters so the purpose of the loop filter is to filter out the high-frequency components from the output of the PFD. Typically, loopfilters are just simple passive RC networks whose main objective is to filter out the high-frequency noise data from the PFD output.

### 3.2.4 Voltage Controlled Oscillator (VCO)

VCOs are the most important and complex component of the overall PLL design. The essential idea behind a VCO design is to generate a clock signal based on the Barkhausen criteria for oscillation which states that the magnitude of the VCO transfer function at the oscillation-frequency is 1 while the phase is -180 degrees. Two most popular VCO topologies whose sample architectures are ring-based and LC-tank based. Due to the superior noise performance we chose to design a LC-Tank based VCO. VCO is the device that generates the target clock. Ideally, its output frequency should be linearly related to the input control voltage. The Laplace transform function of the VCO is derived as follows:

$$\omega_{out}(t) = K_{VCO}v_{ctrl}(t) \tag{3.3}$$

$$\mathcal{L}[\omega_{out}(t)] = \omega_{out}(s) = K_{VCO}v_{ctrl}(s)$$

(3.4)

$$\phi_{out}(t) = \int_{0}^{t} \omega_{out}(\tau)d\tau = \int_{0}^{t} K_{VCO}v_{ctrl}(\tau)d\tau$$

(3.5)

$$\mathcal{L}[\phi_{out}(t)] = \phi_{out}(s) = \frac{\omega_{out}(s)}{s} = \frac{K_{VCO}v_{ctrl}(s)}{s}$$

(3.6)

Thus, the Laplace transform function for the VCO is:

$$H_{VCO}(s) = \frac{\phi_{out}(s)}{v_{ctrl}(s)} = \frac{K_{VCO}}{s}$$

(3.7)

The  $K_{VCO}$  is defined as the VCO gain.

#### 3.2.5 Divider

A frequency divider is needed to produce a clock signal that runs many times faster than the reference clock. The PFD input clock and reference clock have to be synchronized for PLL to be in locked condition. In order to perform this task we use a fractional-N divider circuit, which divides the VCO clock by the highest power of 2 factor to synchronize reference clock signal and the divider output clock.

### 3.2.6 Analysis of a PLL in Locked-State

The open-loop transfer function of the PLL is equal to  $H_O = K_{PD}G_{LPF}(s)\frac{K_{VCO}}{s}$ , yielding the closed-loop transfer function  $H(s) = \frac{\Phi_{out}(s)}{\Phi_{in}(s)} = \frac{K_{PD}K_{VCO}G_{LPF}(s)}{s+K_{PD}K_{VCO}G_{LPF}(s)}$ . In its simplest form, a low pass filter is implemented to have the transfer function  $G_{LPF}(s) = \frac{1}{1+\frac{s}{\omega_{LPF}}}$ , where  $\omega_{LPF} = \frac{1}{RC}$ . Thus, for a PLL containing a first-order LPF the closed-loop response is represented as  $H(s) = \frac{K_{PD}K_{VCO}}{\frac{s}{\omega_{LPF}}+s+K_{PD}K_{VCO}}$  indicating that the system is of second-order, where one pole is contributed by the VCO and the other by the LPF. Here,  $K = K_{PD}K_{VCO}$  is called the loop-gain and expressed in rad/s. In order to understand the dynamic behavior of the PLL, the denominator of the second-order closed-loop response is converted to a form commonly used in control theory:  $s^2 + 2\zeta\omega_n s + \omega_n^2$ , where  $\zeta$  is the damping factor and  $\omega_n$  is the natural frequency of the system. Therefore, the closed-loop response can now be expressed as  $H(s) = \frac{\omega_n^2}{s^2+2\zeta\omega_n s+\omega_n^2}$ , where  $\omega_n = \sqrt{\omega_{LPF}K}$  and  $\zeta = \frac{1}{2}\sqrt{\frac{\omega_{LPF}}{K}}$ . Note that  $\omega_n$  is the geometric mean of the -3dB bandwidth of the LPF and

the loop-gain, and thus an indicator of the gain-bandwidth product of the loop. The damping factor is inversely proportional to the loop gain. Typically, in a well designed second order system,  $\zeta$  is usually greater than 0.5 and preferably equal to  $\frac{\sqrt{2}}{2}$  so as to provide an optimally flat response. Thus, K and  $\omega_{LPF}$  cannot be chosen independently; for example if  $\zeta = \frac{\sqrt{2}}{2}$ , then  $K = \frac{\omega_{LPF}}{2}$ . If  $s \to 0$ , we note that  $H(s) \to 1$ ; i.e. a static phase shift at the input is transferred to the output unchanged. We can examine the "phase error transfer function" defined as  $H_e(s) = 1 - H(s) = \frac{\Phi_e(s)}{\Phi_{in}(s)} = \frac{s^2 + 2\zeta\omega_n s}{s^2 + 2\zeta\omega_n s + \omega_n^2}$  which drops to 0 as  $s \to 0$  [15].

#### 3.2.7 PLL Characteristics and Figures of Merit

The most important metrics of a PLL are Order, Type, Hold-In range, Lock-in range, and Pull-in range. The order of a PLL is determined by the number of poles in the loop while the type is determined by the number of integrators. The VCO always has a pre-existing pole because it generates frequency from phase via an integration; thus every PLL is at least of order 1 and type 1. As the loop-filter poles increases and the PLL order and type increases as well and higher the type, the better the PLL is at tracking both frequency and phase. For instance, a type 2 PLL is capable of tracking both a step change in phase as well as frequency with zero steady-state phase error while a type 1 PLL can only track a step change in phase.

Hold-In range of a PLL is a measure of the DC loop gain and the range of frequencies under which the PLL can maintain a lock. Lock-In range is a measure of the range of frequencies under which a PLL can acquire lock without slipping any clock-cycles. Finally, the Pull-In range is the measure of the range of frequencies for which the PLL can acquire lock by missing a few clock cycles. It is important to note that the hold-in range is the largest of the three and lock-in range is the smallest of the three metrics.

# CHAPTER 4

# PLLs IN CLOCKING CIRCUITS

# 4.1 Charge-Pump (CP) PLLs Overview

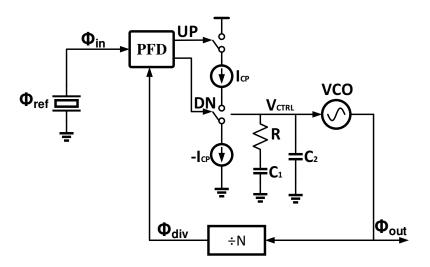

Figure 4.1: Charge-Pump PLL Block Diagram

Figure 4.1 shows the basic building blocks of a CPLL. Charge-Pump PLLs offer many advantages over the classical voltage phase-detector PLL including an infinite pull-in range and zero steady-state phase error. CPLLs also allow one to use a passive filter and still have many of the benefits of using an active filter with the voltage phase detector. The exception to this case is when the VCO tuning voltage needs to be higher than the PLL can supply; in this case, an active filter is necessary [15].

Phase-frequency detectors with charge-pump combination offer several advantages over the voltage charge pump and have all but replaced it. The PFD and CP blocks are universally present in every PLL based synthesizer chip. Using this approach completely bypasses issues of steady-state phase error and hold-in range [10].

## 4.2 CPLL Linear Model and Analysis

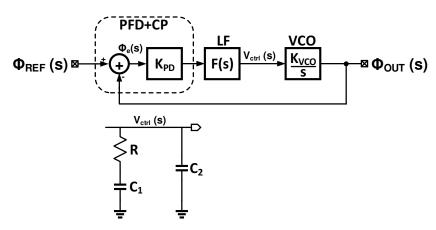

Figure 4.2: Linear s-Domain Model for Charge-Pump PLL

Figure 4.2 shows the linear s-domain model for CPLLs. From the previous section we can now define the open loop transfer function as follows:

$$LG(s) = K_{PD} \cdot F(s) \cdot \frac{K_{VCO}}{s}$$

(4.1a)

$$= K_{PD} \cdot K_{VCO} \cdot \frac{s + \frac{1}{RC_1}}{C_2 s^2 \left(s + \frac{C_1 + C_2}{RC_1 C_2}\right)}$$

(4.1b)

From the open loop gain we notice that

$$\omega_z = \frac{1}{RC_1}; \ \omega_{p1} = \omega_{p2} = 0; \omega_{p3} = \frac{C_1 + C_2}{RC_1C_2}$$

(4.2)

The phase margin will be:

$$\phi_M = \arctan\left(\frac{\omega_{ugb}}{\omega_z}\right) - \arctan\left(\frac{\omega_{ugb}}{\omega_{p3}}\right)$$

(4.3)

where  $\omega_{ugb}$  is the open loop unity gain bandwidth and  $\omega_z < \omega_{ugb}$ .

In order to achieve maximum phase margin, the value of  $C_1$  and  $C_2$  have to be chosen carefully. To calculate the expression of  $\phi_{M\_max}$  we take the first order derivative of Eq. 4.3 with respect to  $\omega_{ugb}$  and equate the result to zero, such that:

$$\omega_{ugb} = \omega_z \sqrt{\frac{C_1}{C_2} + 1} \tag{4.4}$$

Subsequently,

$$\phi_{M\_max} = \arctan(\sqrt{\frac{C_1}{C_2} + 1}) - \arctan(\frac{1}{\sqrt{\frac{C_1}{C_2} + 1}})$$

(4.5)

The design procedure of the loop filter is as follows:

1. Choose desired bandwidth  $\omega_{ugb}$ , phase margin  $\phi_M$  and resistor R according to specification. Then calculate the  $K_c$  from Eq. 4.6:

$$K_c = \frac{C_1}{C_2} = 2(\tan^2(\phi_M) + \tan(\phi_M \sqrt{\tan^2(\phi_M) + 1}))$$

(4.6)

2. From Eq. 4.4 we have:

$$\omega_z = \frac{\omega_{ubg}}{\sqrt{\frac{C_1}{C_2} + 1}} \tag{4.7}$$

$$C_1 = \frac{1}{\omega_z R}; C_2 = \frac{C_1}{K_c};$$

(4.8)

3. From aforementioned equations, we can determine the value for  $I_{CP}$ :

$$I_{CP} = \frac{2\pi C_2}{K_{VCO}} \cdot \omega_{ugb}^2 \cdot \sqrt{\frac{\omega_{p3}^2 + \omega_{ugb}^2}{\omega_z^2 + \omega_{ugb}^2}}$$

(4.9)

It is vital to analytically confirm that the PLL will indeed lock when there is a frequency step applied at the input. Without loss of generality assume there is input frequency step  $\omega_{in} = \frac{\Delta\omega}{s}$ , then  $\Phi_{in}(s) = \frac{\Delta\omega}{s^2}$ . First, obtain the closed loop transfer function:

$$H_{PLL}(s) = \frac{LG(s)}{1 + LG(s)} \tag{4.10}$$

Lastly, define steady state error transfer function:

$$\frac{\Phi_{error}(s)}{\Phi_{in}(s)} = H_e(s) = 1 - H_{PLL}(s) = \frac{1}{1 + LG(s)}$$

(4.11)

Applying the final value theorem, we get the steady state error to be:

$$\Phi_{ss\_error}^{F_{step}} = \lim_{s \to 0} s \cdot H_e(s) \cdot \Phi_{in}(s)$$

(4.12a)

$$= \lim_{s \to 0} s \cdot \frac{1}{1 + LG(s)} \cdot \frac{\Delta\omega}{s^2} \tag{4.12b}$$

$$= \lim_{s \to 0} \frac{[RC_1C_2s^2 + (C_1 + C_2)s]\Delta\omega}{RC_1C_2s^3 + (C_1 + C_2)s^2 + K_{VCO}K_{PD}s + 1}$$

(4.12c)

$$=\frac{0}{1}\tag{4.12d}$$

$$=0 (4.12e)$$

Eq. 4.12(a) to 4.12(e) indicate that the PLL we have designed can eliminate any steady state phase error and relock when a frequency step is applied at the input [8].

## 4.3 CPLL Noise-Analysis

The following equations describe the noise-transfer functions of the CPLL and are used in determining the optimal PLL BW.

$$NTF_{IN}(s) = \frac{\Phi_{OUT}(s)}{\Phi_{IN}(s)} = \frac{N \cdot LG(s)}{1 + LG(s)}$$

(4.13)

$$NTF_{DIV}(s) = NTF_{IN}(s) (4.14)$$

$$NTF_{CP}(s) = \frac{\Phi_{OUT}(s)}{i_{CP}(s)} = \frac{2\pi}{I_{CP}} \cdot NTF_{IN}(s)$$

$$(4.15)$$

$$NTF_R(s) = \frac{\Phi_{OUT}(s)}{v_R(s)} = \frac{\frac{K_{VCO}}{s}}{1 + LG(s)}$$

(4.16)

$$S_{\Phi_{OUT}}^{\Phi_{IN}} = S_{\Phi_{IN}} |NTF_{IN}(s)|^2$$

(4.17)

$$S_{\Phi_{OUT}}^{i_{CP}} = S_{i_{CP}} |NTF_{CP}(s)|^2$$

(4.18)

$$S_{\Phi_{OUT}}^{v_R} = S_{v_R} |NTF_R(s)|^2 \tag{4.19}$$

$$S_{\Phi_{OUT}}^{\Phi_{VCO}} = S_{\Phi_{VCO}} |NTF_{VCO}(s)|^2$$

$$(4.20)$$

$$G_{LPF}(s) = \frac{1}{1 + \frac{s}{\omega_{LPF}}}$$

(4.21)

$$H(s) = \frac{K_{PD}K_{VCO}}{\frac{s}{\omega_{LPF}} + s + K_{PD}K_{VCO}}$$

$$\tag{4.22}$$

$$s^2 + 2\zeta\omega_n s + \omega_n^2 \tag{4.23}$$

$$H(s) = \frac{\omega_n^2}{s^2 + 2\zeta\omega_n s + \omega_n^2} \tag{4.24}$$

$$\omega_n = \sqrt{\omega_{LPF}K}, \zeta = \frac{1}{2}\sqrt{\frac{\omega_{LPF}}{K}}$$

(4.25)

$$\zeta = \frac{\sqrt{2}}{2}, \implies K = \frac{\omega_{LPF}}{2}$$

(4.26)

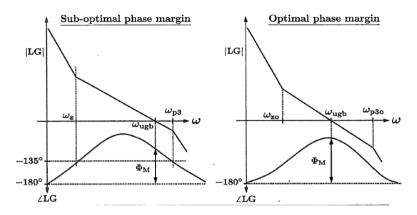

Figure 4.3: Loop-Gain and Phase-Margin Response

Figure 4.4: CPLL Output Noise Model

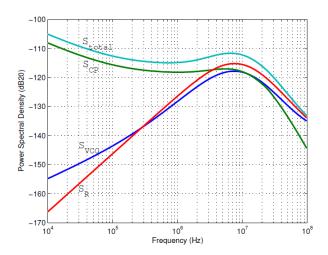

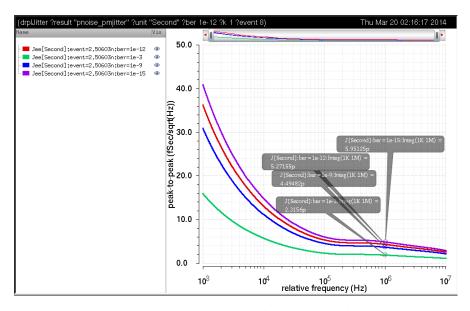

Figure 4.5: CPLL Output Noise Simulation

Figure 4.3 [8] shows the typical loop-gain and phase-margin plot for a CPLL. Recall that phase-margin is the difference in phase between  $-180\,^{\circ}$ C and the phase value corresponding to  $\omega_{ugb}$ . Figure 4.4 shows the typical noise-profile for each component in a CPLL based Integer-N synthesizer [12]. Figure 4.5 shows the noise-transfer function characterization for the PLL using the above equations implemented in MATLAB. The beauty of this analysis is that it accurately predicts what the noise-profile for the PLL will look like so that the designer can determine the BW specifications for the PLL from which the rest of the Loop-Filter and VCO specifications can be determined.

# CHAPTER 5

# PLL BASED CLOCK GENERATOR

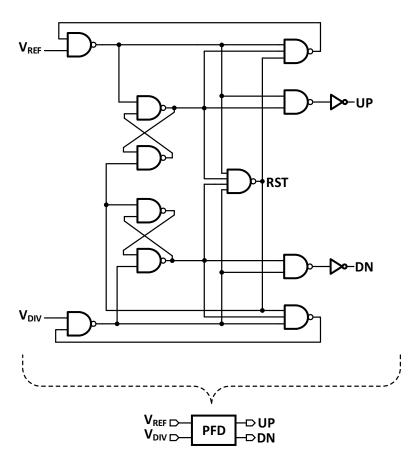

### 5.1 PFD

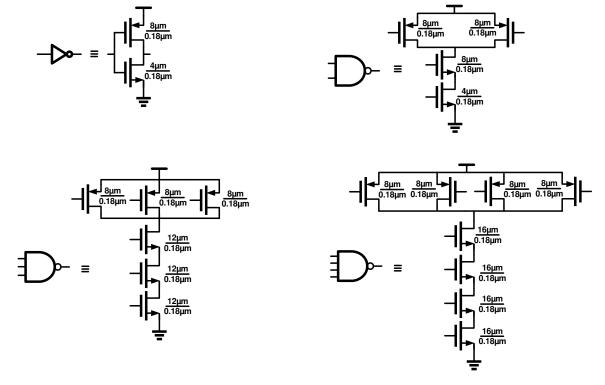

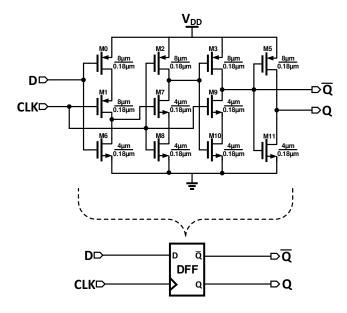

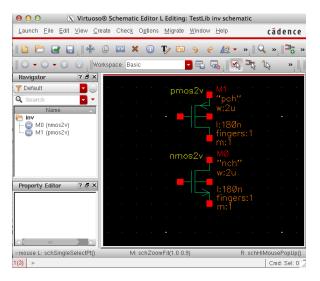

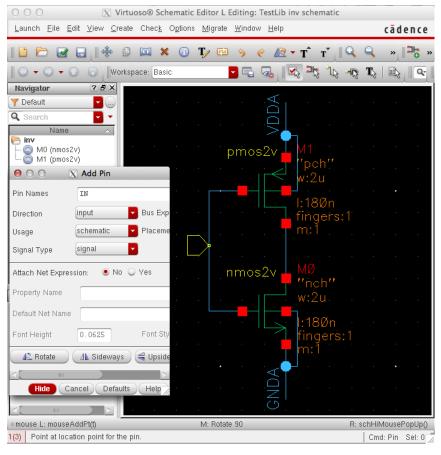

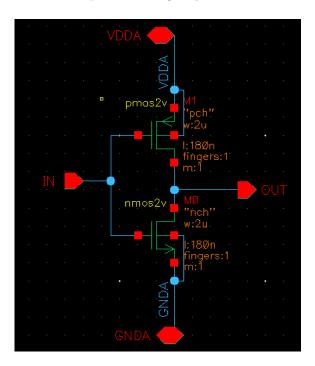

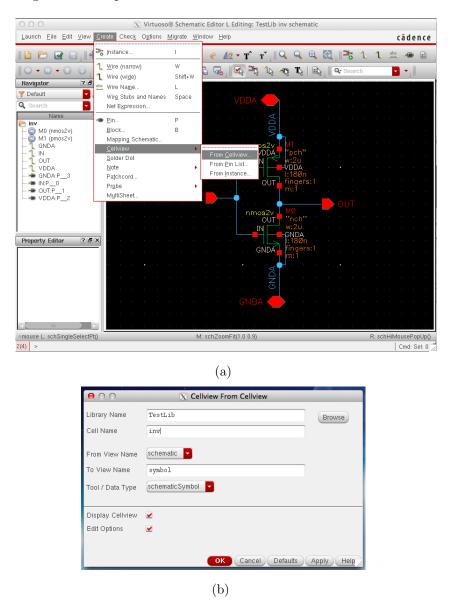

Figure 5.1 shows the NAND PFD implementation used in the design of the PLL used in this thesis. In Figure 5.2 the transistor-level implementation for each of the circuits shown in Figure 5.1 are displayed with the appropriate sizing.

Figure 5.1: NAND PFD Implementation

Figure 5.2: PFD Transistor Level Circuit Blocks

One of the major challenges during the design of an efficient PFD circuit is the "dead-zone" problem. "Dead-zone" is refers to the region wherein there is no output for inputs. It is equal to the sum of the on-times of the pullup/pull-down switches in the charge-pump and is typically a problem because the presence of dead-zone causes the PLL to operate in "open-loop" when the phase-error is zero. One method to overcome the dead-zone issue is to ensure that the PFD generates equal UP/DN pulses whose width is larger than the switch-on time of the CP switches. The NAND-PFD implementation is one example of a PFD circuit where the dead-zone issue is avoided. The D-Flip-Flops are designed using cross-coupled NAND-latches and even though this uses up a lot of on-chip area and burns a lot of power in the PFD circuit, the large delay in UP/DN feedback paths allows the pulse-widths to be just larger than the switch-on time of the PMOS/NMOS transistors that act as the pullup/pull-down switches in the CP. The maximum operating frequency of a PFD circuit is determined by the reset path delay such that  $F_{max} < \frac{1}{2T_{RST}}$ . In the case of a NAND PFD circuit,  $T_{RST} = 2T_{NAND2} + T_{NAND4}$ , where we intentionally design the NAND4 circuit to have a high delay to minimize the reset period.

### 5.2 CPs

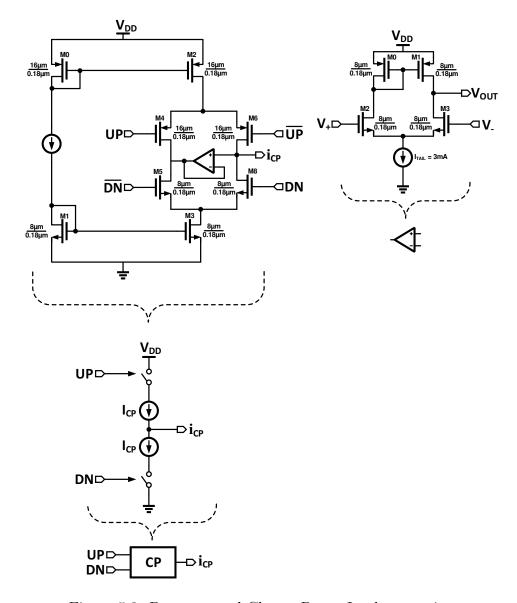

Figure 5.3 shows the CP implementation used in the design of the PLL used in this thesis. The transistor-level implementation is also displayed with the appropriate sizing.

Figure 5.3: Bootstrapped Charge-Pump Implementation

The charge-pump circuit needs to be carefully designed in because it is the main contributor to low-frequency PLL noise. The current mismatch in the charge-pump leads to static-phase offset and causes ripples in the control voltage, thereby creating a 'jittery' VCO output clock. Thus, it is important to design a CP circuit that has equivalent pull-up and pull down currents and equal on-time for the PMOS/NMOS switches. Though several CP architectures exist, a 'Bootstrapped' CP design is used in the clock-generating PLL studied in this thesis. The advantage of the Bootstrapped architecture is that it allows differential current steering, it can operate with low-swing UP, DN signals. It is thus very prominent in PLLs that use high-speed reference clock signals. The term 'bootstrapped' are appropriate because the voltage following op-amp between the pull-up and pull-down current networks ensures that an equal voltage level is maintained on either ends such that the pull-up current is equal to the pull-down current.

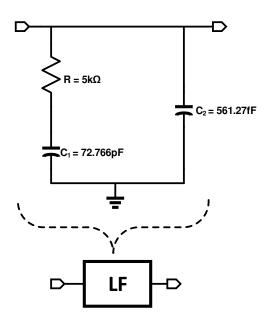

#### 5.3 LF

Figure 5.4: Loop-Filter Implementation

Loop-Filter is designed using the design-procedure described in Chapter 4 in the CPLL design procedure algorithm. The algorithm was implemented in MATLAB to choose the values shown above in Figure 5.4.

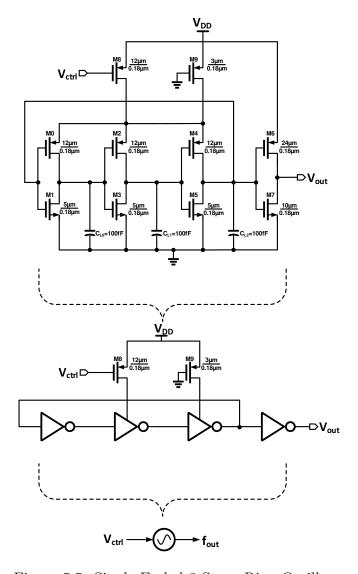

#### 5.4 VCOs

Figure 5.5: Single-Ended 3-Stage Ring Oscillator

A 3-Stage ring-oscillator is implemented with a driver inverter (as shown in Figure 5.5 with full transistor-level sizing) whose size is fixed such that the input capacitance seen by the divider remains constant while the VCO frequency is changing. M8 and M9 act as the pull-up resistors, i.e. they are PMOS transistors that are biased to be in triode/resistive region. In order to ensure the oscillation starts, the gate of M9 is driven to ground while gate of M8 is driven by the control voltage which alters the phase-delay between the ring to vary to the oscillation frequency.

#### 5.5 Divider

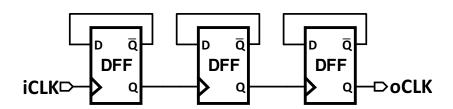

Figure 5.6: TSPC Based D Flip-Flop Architecture

Figure 5.7: Divider Architecture

The divider circuit consists of 3-DFFs that are connected together in the manner shown in Figure 5.7 to realize a divide-by-8 operation. Division in binary is essentially a left-shift operation; thus, tying the outputs of each DFF to clock input of the next while connecting the input to the inverse of output in a feedback ensures a left-shift operation. Since the PLL output frequency is in the GHz range, the DFF design is very critical. To realize a fast DFF with low clock-skew and delay a TSPC (True-Single Phase Clock) architecture (as shown in Figure 5.6) is employed. The basic idea is that when CLK is high transistors M1 and M9 are ON/OFF respectively and vice versa, thereby preserving the state except when CLK goes from low to high, in which case the output follows the data-input signal denoted by D.

# CHAPTER 6

# BEHAVIORAL LEVEL SIMULATION

### 6.1 Why Behavioral Modeling?

Traditionally SPICE is used as a common simulation engine to simulate analog/mixed-signal circuit. However, when simulating large networks the simulation times can become extremely long, thereby limiting the allowed design revisions to the circuit designer. It is very tedious to describe the behavior of a circuit using SPICE unless the complete physical transistorlevel structure of the circuit is known to the designer. Furthermore, the SPICE simulation process is very technology dependent in that with technology scaling the SPICE models need to be updated as the older models become obsolete and invalid for accurate simulation. The aforementioned design process has remained virtually the same over the past few decades and even though the digital design synthesis process has progressed significantly by incorporating electronic system-level (ESL) design automation techniques, the mixed signal design process is very slow, laborious and therefore errorprone. Digital design engineers, though working with millions of transistors, have been able to automate the design flow, but analog designers have been unable to do so even though most analog circuits only consist of tens of thousands of devices.

### 6.2 Why Verilog-AMS?

Verilog-AMS is a high-level Hardware Description Language (HDL) used to describe the structure and behavior of analog and mixed-signal systems. It is an extension to the IEEE 1364 Verilog HDL standard and is very powerful in providing fast prototyping capabilities for mixed-signal systems. The

key advantage of circuit modeling using Verilog-AMS is that it provides a single language and simulator ecosystem that can be shared between analog, digital and system-level designers. Verilog-AMS leverages the superior speed and capacity offered by traditional Verilog and allows event-driven capabilities within analog model simulation, making it an attractive choice when simulating highly complex mixed-signal circuits such as PLLs, CDRs, ADCs, and DACs. The only pitfall of using Verilog-AMS is that it cannot replace traditional transistor level SPICE simulation completely as it does not have synthesis capabilities like its digital counterpart Verilog. However, at the onset of the design phase, using Verilog-AMS for circuit modeling is very powerful for a mixed-signal circuit/system design engineer as it offers fast prototyping/verification for behavioral level simulation, thereby expediting the time-to-market for the system.

Verilog-AMS combines both Verilog-D and Verilog-A including a few additional mixed-signal constructs to provide a HDL language capable of performing truly mixed-signal simulation. Cadence has been the front-runner in promoting the language making it an industry standard, and has led the majority of the advancement efforts ever since its release in 2003. The power of Verilog-AMS simulator in Cadence Virtuoso is that it can perform cosimulation among behavioral analog/digital blocks described by corresponding Verilog-A and Verilog-D models respectively as well as transistor-level circuit blocks by running the Spectre simulation. When a circuit consisting of transistor-level circuit elements, analog behavioral modules written in Verilog-A and digital behavioral modules written in Verilog-D is simulated, the AMS simulator in Cadence partitions the testbench into analog and digital components. The simulator then merges the analog simulation results from Spectre with the digital simulation results from NC-SIM and the resulting output is plotted just like that in the case of traditional Spectre simulation [4].

# 6.3 Basic Verilog-A/AMS Syntax

A typical skeleton of a Verilog-AMS code is shown in Figure 6.1 where the main components of a Verilog-A/AMS code are listed.

```

1 `include "disciplines.vams"

2

3 module name(inputs,outputs)

parameter real var = 0;

4

5

input in1;

6

output out1, out2;

7

electrical out1,out2;

8

9

analog

10

begin

11

----code logic----

12

13

14

end

15 endmodule

```

Figure 6.1: Verilog-AMS Sample Code

In the first line of the sample code shown in Figure 6.1 [4], we include the 'disciplines.vams' header file. This file is a collection of physical signal types that are commonly used in Verilog-AMS and are thus referred to as 'natures'. Electrical disciplines consist of 'voltages' and 'currents' and are used most commonly during mixed-signal system modeling where 'voltage' and 'current' are 'natures'. Every Verilog-AMS component is defined as a 'module' and modules are the basic building blocks of any given Verilog-AMS files as they describe the component being modeled. Ports are the points where connections are made to the given component. Every port is required to have a direction associated with it, and by default in Verilog-AMS language there are three types of ports: input, output and inout. The keyword **electrical** signifies that the signals associated with the ports described as electrical are of 'voltage' and 'current' natures. Additionally, analog is the keyword after which point the Verilog-AMS compiler starts actual modeling as the logic/process starts after the 'analog begin'. Finally, every Verilog-AMS component code should end with the word **endmodule** as it signifies the point at which the compiler stops parsing of the code [4].

# 6.4 PLL Simulation in AMS Using Cadence Virtuoso

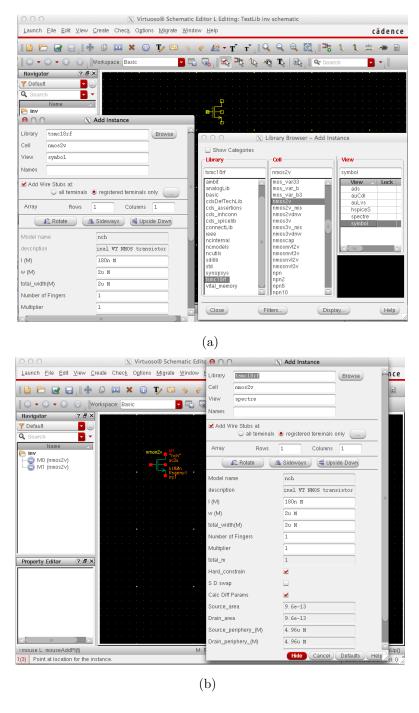

### 6.4.1 PFD+CP

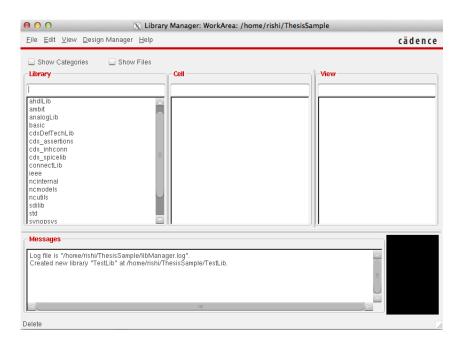

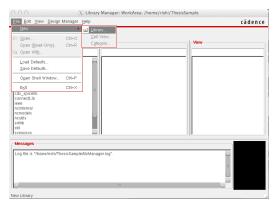

- 1. Create a new library and name it 'PLLBehav'. Now within the Library Manager window, click on File → New → Cell View and call the new VerilogAMS file pfd. Choose the 'VerilogAMSText' option from the drop-down Menu as shown in Figure 6.2. Click 'OK' and a text editor window will open up.

- 2. Figure 6.3 shows the 'PFD' code used in the design. The PFD is a completely digital circuit; thus, this code is essentially in Verilog-D syntax where the UP, DN signals are generated by comparing the rising edges of the flip-flops that have a CLK signal of  $F_{REF}$  and  $F_{DIV}$  respectively.

Figure 6.2: PFD Verilog-AMS Code Setup

```

1 //Verilog-AMS HDL for "BehavPLL", "pfd" "verilogams"

`include "constants.vams"

`include "disciplines.vams

5 `timescale 10ps / 1ps

7 module pfd (up,dn,upb, dnb,fref,fdiv);

input fref;

input fdiv;

output up, upb, dn, dnb;

13 wire fv_rst, fr_rst;

15 reg q0, q1;

16

17 assign fr_rst = reset | (q0 & q1);

18 assign fv_rst = reset | (q0 & q1);

19 assign reset = fref & fdiv;

21 always @ (posedge fdiv or posedge fv_rst) begin

24 always @ (posedge fref or posedge fr_rst) begin

27 assign up = q1;

28 assign dn = q0;

29 assign upb = ~q0;

30 assign dnb = ~q1;

31 endmodule

```

Figure 6.3: PFD Verilog-AMS Code

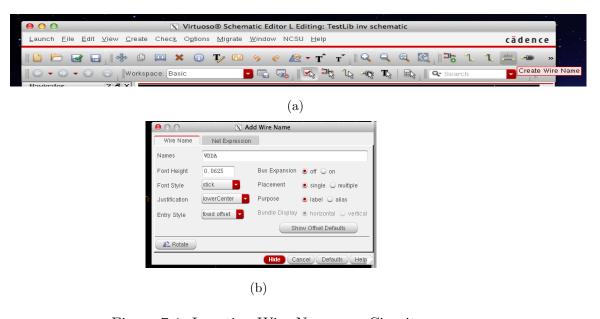

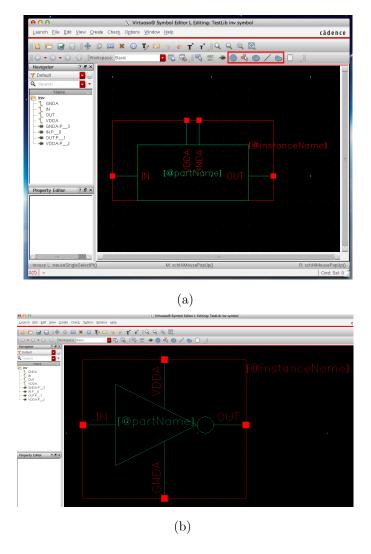

3. Once you have written the code as shown in Figure 6.4, save and exit the text editor. A pop-up window like Figure 6.4 will open up. Click 'Yes' to generate the symbol for the 'pfd'.

Figure 6.4: PFD Verilog-AMS Symbol

4. Within the 'PLLBehav' library you created above, click on  $File \rightarrow New \rightarrow Cell\ View$  and call the new schematic  $pfd\_tb$  as shown in Figure 6.5. Double-click on this cell-view and a schematic window will open up.

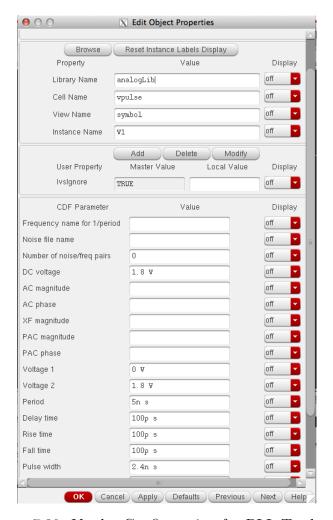

Figure 6.5: PFD Verilog-AMS Schematic

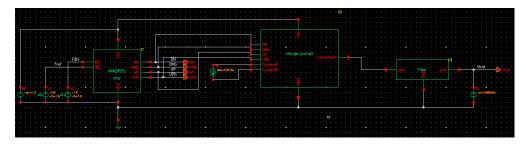

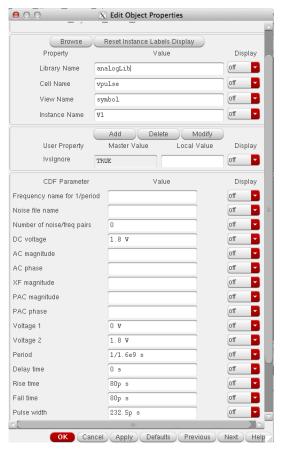

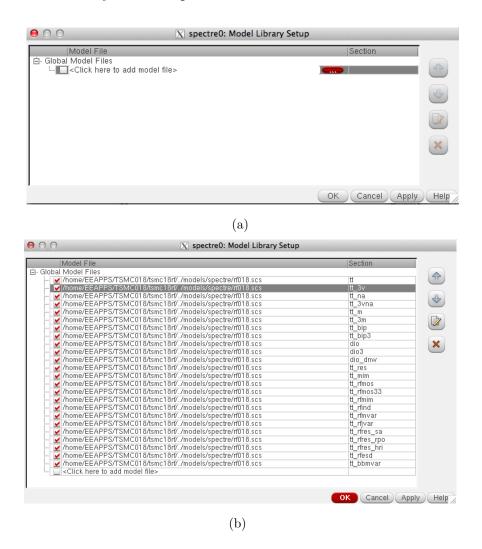

5. In order to create a circuit in the schematic editor, we need to add 'instances' or circuit-components like transistors, supply nets and wires. To add an instance press I from your keyboard. This will open up a 'Component Browser'. Choose the 'PLLBehav' library and within it select the symbol for 'pfd'. Repeat the same process to add the 'vpulse' components found in the 'analogLib' library. Make sure the 'fref' and 'fdiv' sources have a 100ps delay between each other. Figure 6.6 shows what your test-bench schematic should look like.

Figure 6.6: PFD Verilog-AMS Testbench

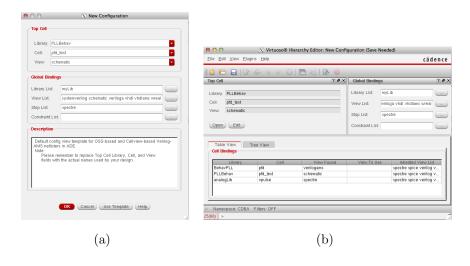

6. When simulating Verilog-AMS files in Cadence Virtuoso, we need to create a 'config' file whose job is to link the analog test-bench sources and the verilog simulation engines together. In order to do so, within the 'pfd\_test' cell-view click on File → New → Cell View and call the new config pfd\_test as shown in Figure 6.7. Double-click on this cell-view and a New Configuration window will open up. Click on 'Use Template', choose the AMS template and configure the setup as shown in Figure 6.8(a). Finally the configuration setup will look like that

shown in Figure 6.8(b), so click on 'Save' and press 'Open'. Now a window like the schematic view will open up but this time it will have config in the title.

Figure 6.7: Config File Creation

Figure 6.8: Config File Setup

- 7. We will simulate our circuits using Cadence AMS Simulation engine. AMS is capable of simulating Verilog-AMS as well as Spectre components. Spectre is a variant of HSPICE developed by Cadence and provides greater accuracy, speed and flexibility especially when dealing with mixed signal circuits.

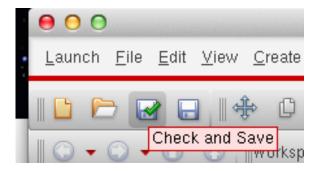

- 8. Make sure you first 'Check and Save' your config file and click on  $Launch \rightarrow ADE$  to open up the ADE window.

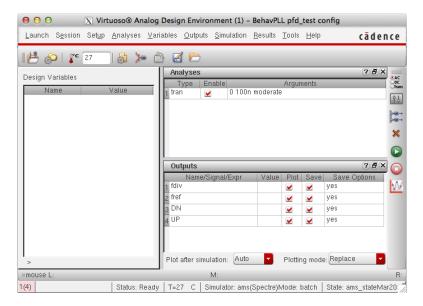

9. Click on Setup o Simulator to make sure the Simulator is set to AMS. Select the output nodes and choose a transient simulation for 100ns as shown in Figure 6.9.

Figure 6.9: PFD Verilog-AMS ADE Outp Window

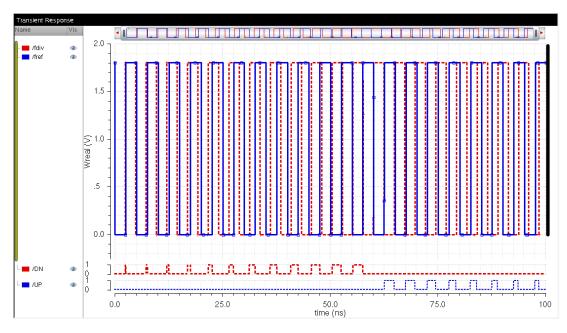

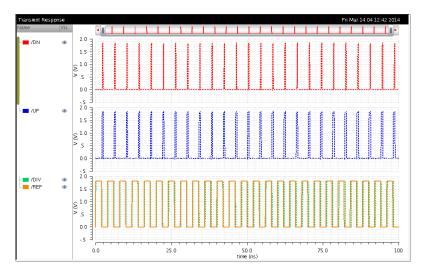

10. In the final output waveform shown in Figure 6.10 it is clear that the PFD is functioning correctly. Notice that the UP,DN pulses are appropriately modulated as 'REF' and 'DIV' signals diverge from one another.

Figure 6.10: PFD Verilog-AMS Simulation Output

11. Within the 'PLLBehav' library follow the steps described earlier to create a model for the CP as shown in Figure 6.11 and save the file as 'cp'.

```

1 //Verilog-AMS HDL for "BehavPLL", "cp" "verilogams"

3

include "constants.vams"

include

"disciplines.vams

timescale 10ps / 1ps

7 module cp (pout, nout, up, dn);

8 parameter real cur = lm; // output current (A)

input up, dn;

output pout, nout;

10 output po

11 electrica

12 real out;

13 analog begin

14 @(initial

15 if (dn

16 o

17 else i

18 o

19 else o

20 I

electrical pout, nout;

real out;

@(initial_step) out = 0.0;

if (dn && !up)

out = -cur;

else if (!dn && up)

out = cur;

se out = \frac{1}{0};

I(pout, nout) <+ -transition(out, 0.0, 10n, 10n);</pre>

22 endmodule

```

Figure 6.11: CP Verilog-AMS Code

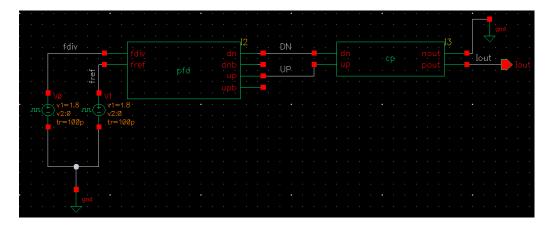

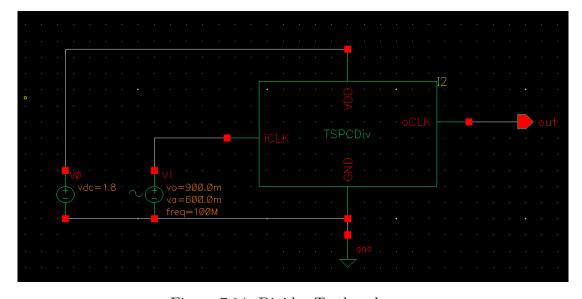

12. Figure 6.12 shows the 'PFD+CP' testbench schematic. Create a new schematic named 'cp\_test' as well as a config file following the same procedure as the PFD. When simulating using the ADE AMS simulator follow the procedure similar to that shown in Figure 6.9.

Figure 6.12: PFD+CP Verilog-AMS Testbench

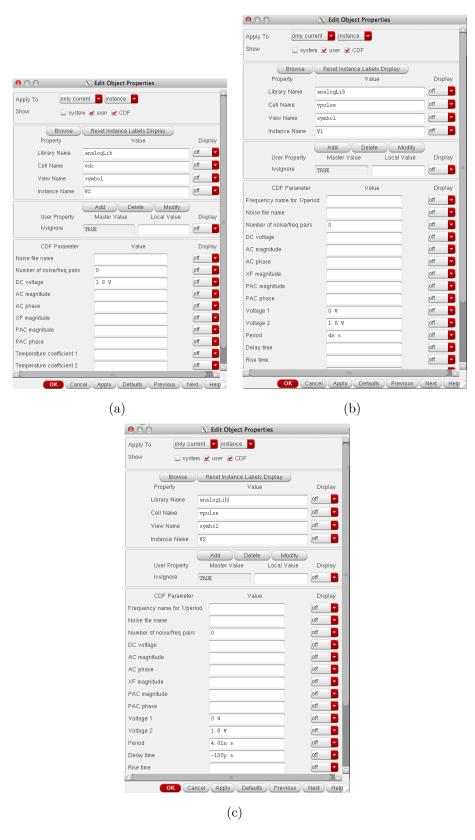

13. One of the powerful advantages of behavioral modeling is that we can easily alter values of design variables to modify the functionality of a block. In the 'config' testbench file if you click on the 'CP' block and press **q**, a window as shown in Figure 6.13 will appear. Enter the appropriate value of charge-pump current as per the design objectives.

Figure 6.13: CP Verilog-AMS Testbench Variable Setup

14. The purpose of the charge-pump is to convert the digital PWM signal outputs from the PFD into a current. As seen in the code and from the final output waveform shown in Figure 6.14, it is clear that the

'PFD+CP' is functioning correctly. When UP is high the current the pull-up current source is on and when DN is high the pull-down current source is on.

Figure 6.14: PFD+CP Verilog-AMS Simulation Output

#### 6.4.2 LF

We use the analog loop-filter as shown in Figure 5.4.

#### 6.4.3 VCO

1. The VCO is the most critical component of the PLL we try to model using Verilog-AMS because it allows us to behaviorally estimate the jitter specifications. Within the 'PLLBehav' library follow the steps described earlier to create a model for the VCO as shown in Figure 6.15 and save the file as 'vco'. Only the white-noise jitter is considered in this design and it is modeled by a Gaussian white-noise probability distribution function.

Figure 6.15: VCO Verilog-AMS Code

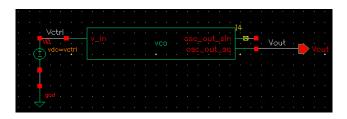

2. Figure 6.16 shows the 'VCO' testbench schematic. Create a new schematic named 'vco\_test' as well as a config file following the same procedure as the PFD. When simulating using the ADE AMS simulator follow the procedure similar to that shown in Figure 6.9.

Figure 6.16: VCO Verilog-AMS Testbench

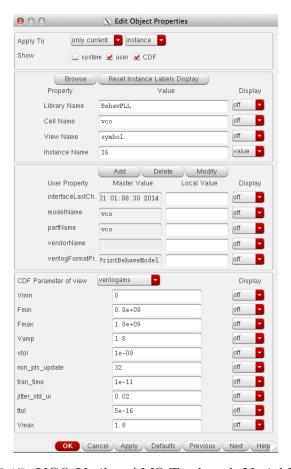

3. Just like in the case of the 'CP' in the 'config' testbench file, if you click on the 'VCO' block and press **q**, a window as shown in Figure 6.17 will appear. Enter the appropriate value VCO design parameters as per the design objectives.

Figure 6.17: VCO Verilog-AMS Testbench Variable Setup

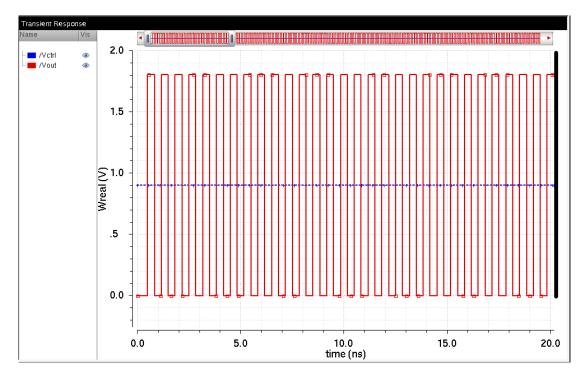

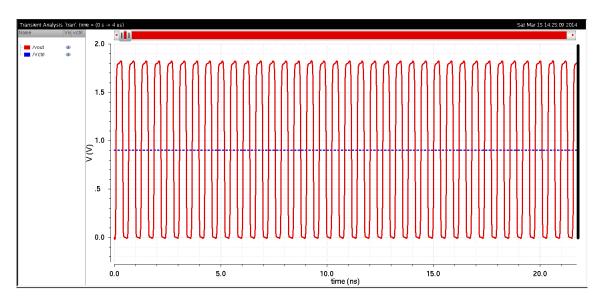

4. The VCO circuit is supposed to generate a periodic square-wave output at the desired frequency of interest (as a function of the control voltage) with a certain jitter level which in our case is chosen to be 2% Unit-Interval (UI) of period. From the final output waveform shown in Figure 6.18 it is clear that the 'VCO' is functioning correctly.

Figure 6.18: VCO Verilog-AMS Simulation Output

#### 6.4.4 Divider

1. Divider is essential when designing a clock-generating circuit as we need to scale down the VCO output clock to the reference frequency level such that the two signals can be compared. Within the 'PLLBehav' library follow the steps described earlier to create a model for the Divider as shown in Figure 6.15 and save the file as 'div'. Figure 6.19 shows the code to implement the divider in Verilog.

```

1 //Verilog-AMS HDL for "BehavPLL", "divider" "verilogams"

`include "disciplines.vams"

timescale 10ps/ 1ps

7 module divider(out,clk);

input clk;

output out;

parameter divide_ratio = 8;

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

reg out;

integer i=0;

always@(posedge clk) begin

if (i < (divide_ratio/2)-1) begin

out = 0;</pre>

i = i + 1;

else if (i == (divide_ratio/2)-1) begin

out = 1;

end

else if (i < (divide_ratio)-1) begin</pre>

end

else if (i == (divide_ratio)-1) begin

out = 0;

end

32 endmodule

```

Figure 6.19: Divider Verilog-AMS Code

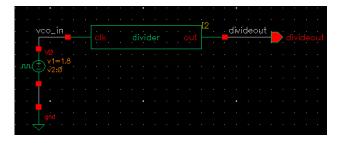

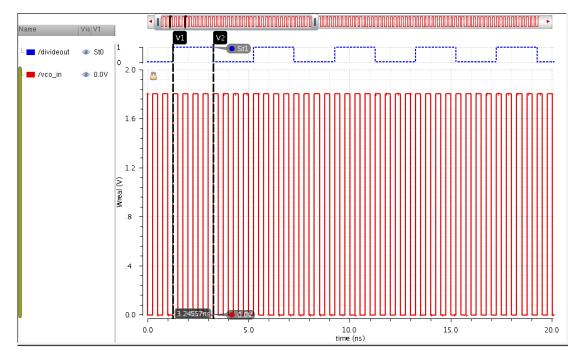

2. Figure 6.20 shows the 'Divider' testbench schematic. Create a new schematic named 'div\_test' as well as a config file following the same procedure as the PFD. When simulating using the ADE AMS simulator follow the procedure similar to that shown in Figure 6.9.

Figure 6.20: Divider Verilog-AMS Testbench

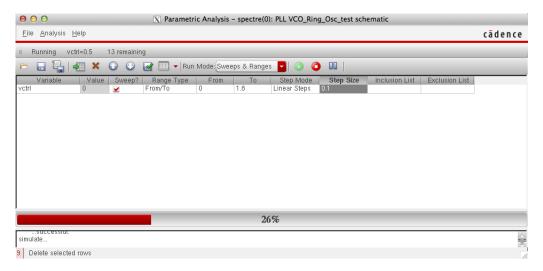

3. Just like in the case of the 'CP and VCO', in the 'config' testbench file if you click on the 'Divider' block and press **q**, a window as shown in Figure 6.21 will appear. Enter the appropriate value of divide ratio as per the design objectives.

Figure 6.21: VCO Verilog-AMS Testbench Variable Setup

4. The divider circuit is supposed to generate a periodic square-wave output that is fraction of the VCO output frequency. From the final output waveform shown in Figure 6.22 it is clear that the 'Divider' is functioning correctly in that it divides the VCO output signal by a factor of 8.

Figure 6.22: Divider Verilog-AMS Simulation Output

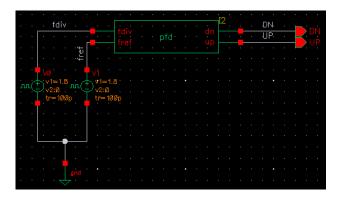

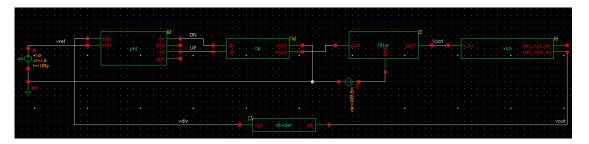

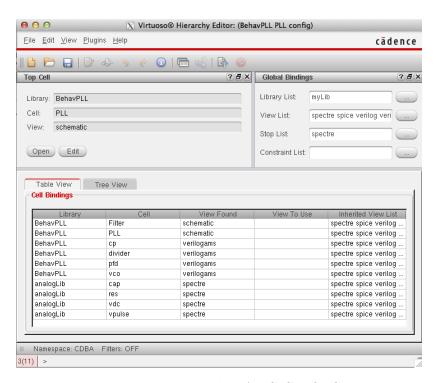

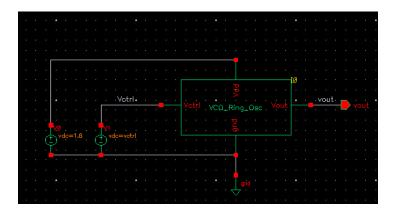

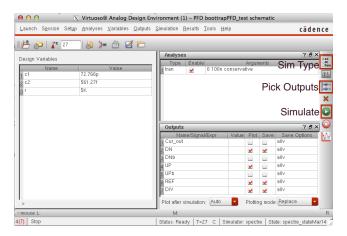

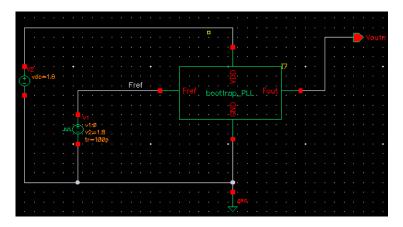

#### 6.4.5 Complete PLL Analysis with Jitter

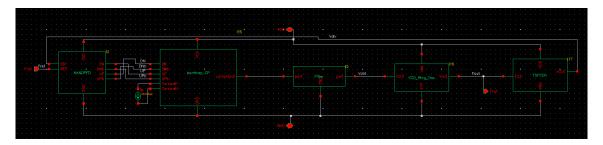

1. Create a new schematic within the 'PLLBehav' library and name it 'PLL'. Your schematic should look that shown in Figure 6.23. Now create a config file for this setup and at the end your configuration window should look like Figure 6.24.

Figure 6.23: PLL Verilog-AMS Testbench

Figure 6.24: PLL Verilog-AMS Config Setup

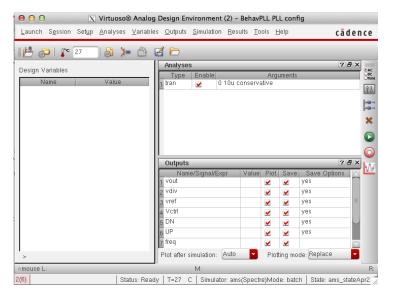

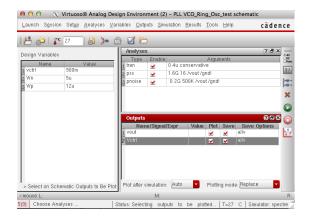

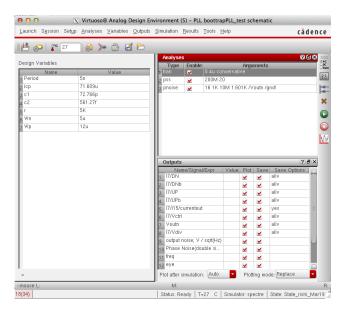

2. Using the steps described earlier in this chapter, configure your ADE window as shown in Figure 6.25 and simulate the circuit.

Figure 6.25: PLL Verilog-AMS ADE Setup

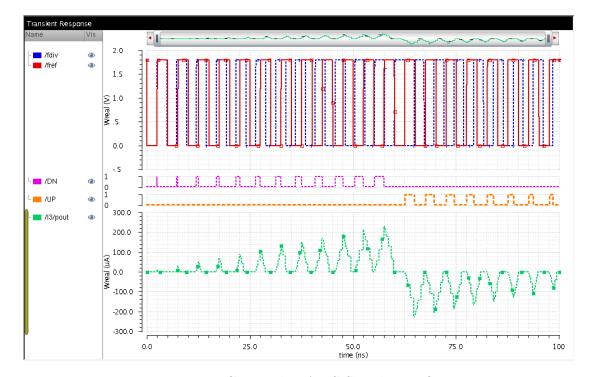

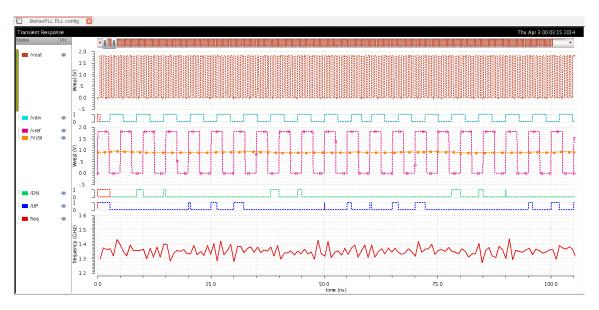

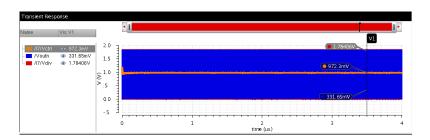

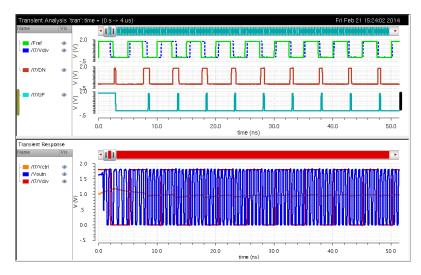

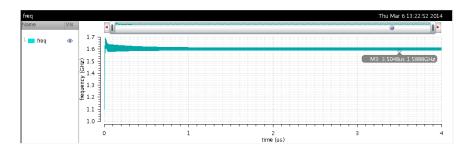

3. The PLL circuit outputs are shown in Figure 6.26. It is clear that the PLL achieves lock within the first 100ns because in the testbench we provide an initial condition of  $V_{ctrl} = 0.9V$  and keep the currents at the loop-filter capacitors at an initial condition of 0A. These initial conditions are provided to ensure that the simulation time is small. From the final output waveforms it is clear that the 'PLL' is indeed functioning correctly.

Figure 6.26: PLL Verilog-AMS Simulation Output

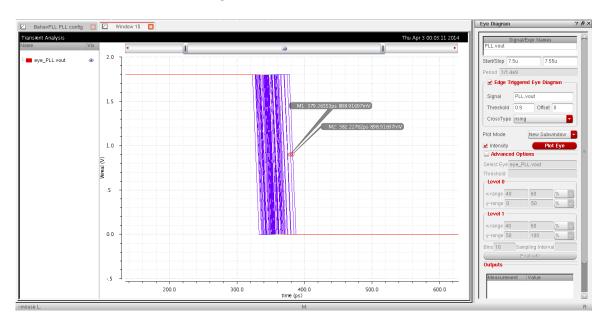

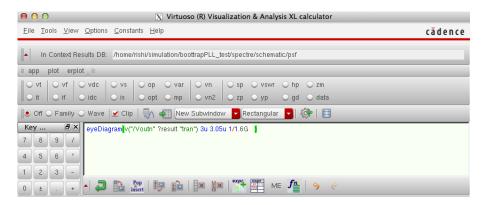

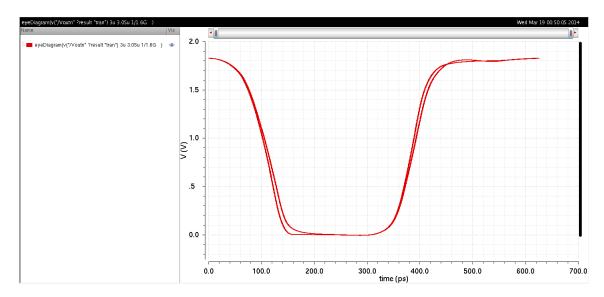

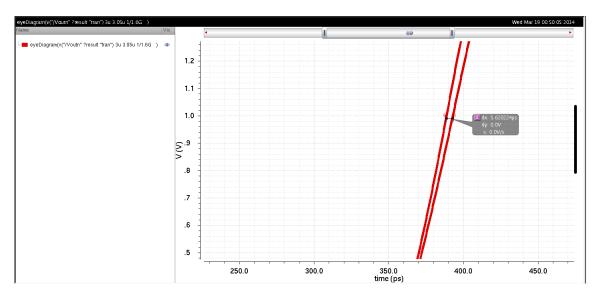

4. To simulate the jitter at the VCO output during lock-condition, select the vout waveform, click on Measurements → EyeDiagram and configure the setup as shown in Figure 6.27. Your final output should look like that shown in Figure 6.27 once you click on 'Plot Eye'. The simulated edge-to-edge jitter is 0.96ps which is extremely good. However, it is important to note that this number is not realistic as we have only accounted for random jitter caused by white-noise and the model is only behavioral so any transistor-level non-idealities are not captured. Nevertheless, behavioral modeling is very powerful in performing rapid prototyping of the PLL circuit elements and performs a system level noise/timing budget for the design before delving straight into transistor level design.

Figure 6.27: PLL Verilog-AMS Jitter

# CHAPTER 7

# TRANSISTOR LEVEL SIMULATION

#### 7.1 What is SPICE?

Simulation Program with Integrated Circuit Emphasis (SPICE) is a general-purpose circuit simulation program that was originally developed at the University of California-Berkeley to serve as a numerical circuit solver that is capable of performing DC, Transient, as well as AC analyses for electronic circuits. The simulator in general is capable of performing the aforementioned analyses on circuits containing resistors, capacitors, inductors, independent voltage and current sources, dependent sources, lossless and lossy transmission lines, switches, uniform distributed RC lines, and the five most common semiconductor devices: diodes, BJTs, JFETs, MESFETs, and MOSFETs. Many variants of SPICE have been developed since with the most popular ones being HSPICE and Spectre.

# 7.2 SPICE vs. Spectre

The Spectre circuit simulator is a variant of SPICE that was developed by Cadence to simulate analog and digital circuits at the differential equation level. Although at a high-level the Spectre and SPICE circuit simulators are quite similar in terms of functionality, Spectre directly is not dependent on SPICE and the two simulators also have differing syntax. The parent algorithms for both are primarily the same in that both use the Modified Nodal Analysis (MNA) method involving implicit integration methods, Newton-Raphson, and direct matrix solution, but the source codes are not borrowed from original open-source SPICE. Spectre is optimized for faster speed as well accuracy compared to SPICE and is thus much more reliable and accurate.

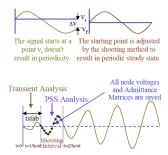

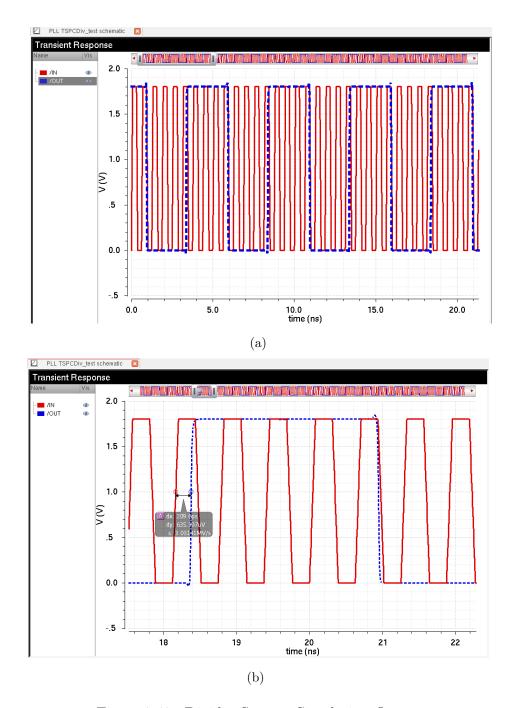

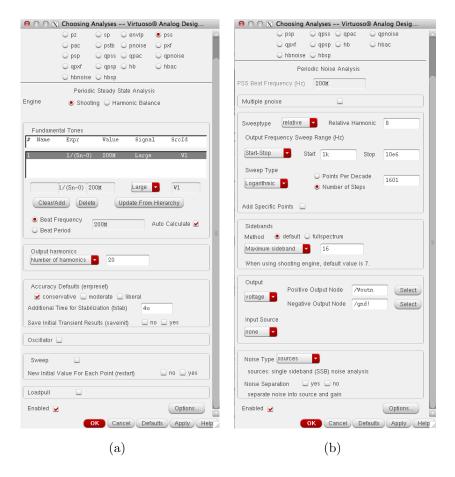

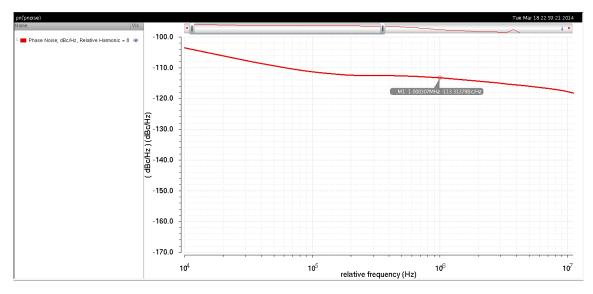

# 7.3 Transient, PSS and PNoise Simulation Overview

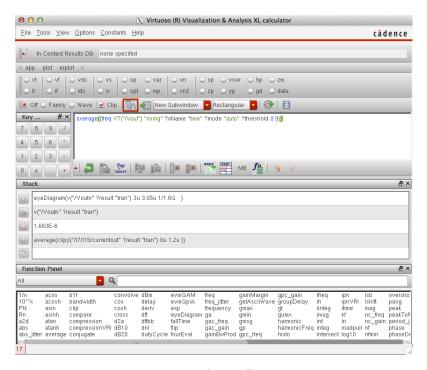

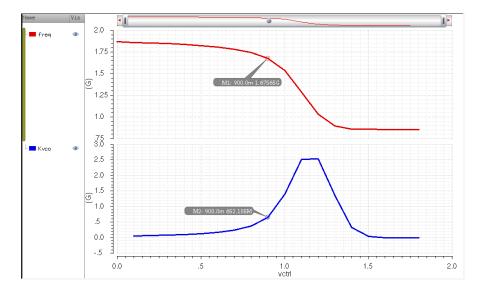

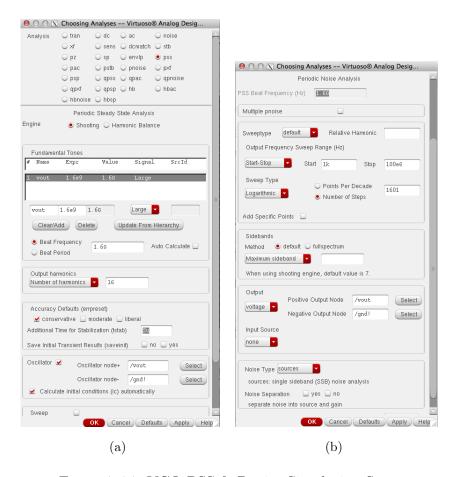

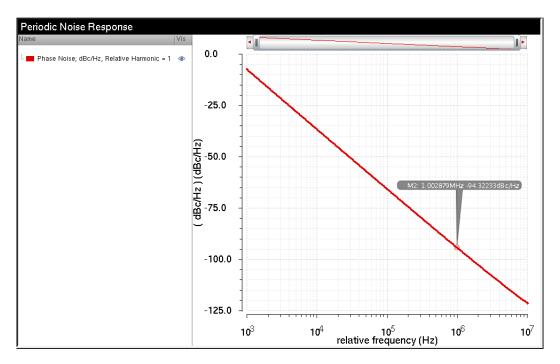

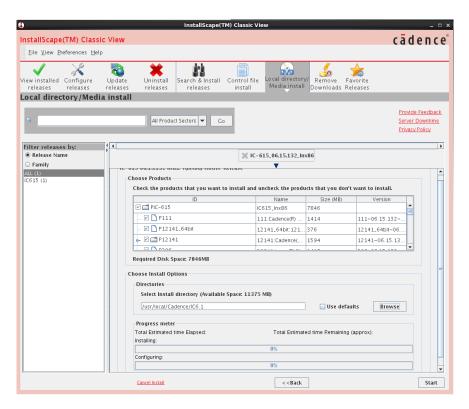

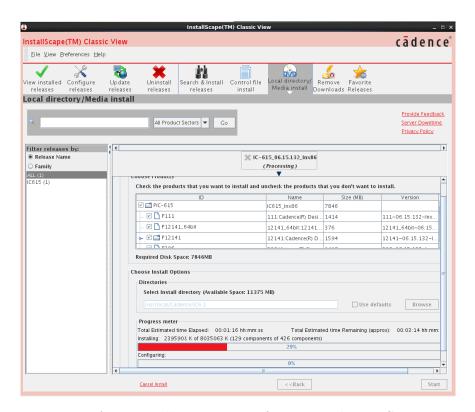

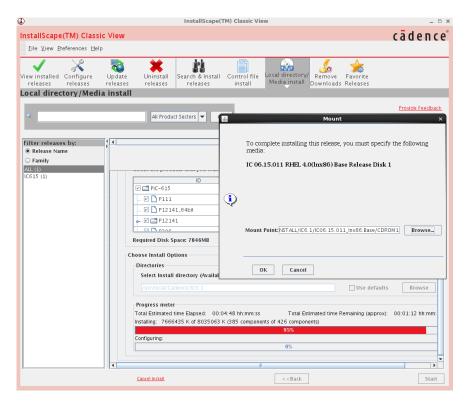

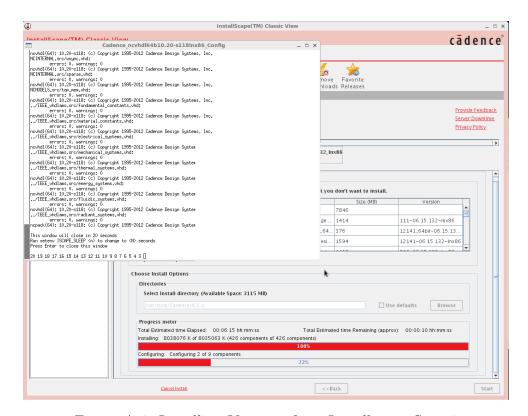

Transient response is the time-domain simulation response for a given circuit and is used to study the time-domain behavior of voltages and currents at any given node in a network. It is a powerful analysis method to study amplifier circuits; however, in the case of oscillators it falls short in being able to accurately characterize the harmonic behavior of the outputs. Thus, to study oscillator, mixer circuits or for that matter any circuit that has a time-varying or periodic nature, the Periodic Steady State (PSS) analysis is the preferred method of simulation.