© 2022 Yixuan Zhao

# MACHINE LEARNING APPROACH FOR CASCADE-ABLE NONLINEAR TRANSCEIVER MODELING AND HIGH SPEED LINK SIMULATION

BY

YIXUAN ZHAO

#### DISSERTATION

Submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy in Electrical and Computer Engineering in the Graduate College of the University of Illinois Urbana-Champaign, 2022

Urbana, Illinois

Doctoral Committee:

Professor José E. Schutt-Ainé, Chair Professor Erhan Kudeki Professor Jennifer T. Bernhard Professor Peter D. Dragic

## ABSTRACT

With the rapid developments in integrated circuit technology, the data rates of chip-to-chip communication are fast approaching several tens of Gb/s. While the desire for massive data-exchange is satisfied as a result of transceiver links operating at high frequency, signal integrity (SI) issues emerge due to short switching times. To identify and resolve these problems early in the production cycle, SI simulations such as time-domain transient analysis are incorporated in pre- and post-layout design stages. For efficiency concern, it is often desired to use accurate and efficient black-box macromodels of components on board instead of their SPICE-like representations. The motivation rests in the nonlinear nature of the transceivers, which oftentimes requires multiple Newton-Raphson iterations before convergence can be achieved. This thesis is meant to contribute a small part to the enormous amount of effort of the behavior modeling community in the quest for computationally efficient methods capable of handling high speed link (HSL) simulation of nonlinear devices and systems using machine learning methods. Specifically, this work reports a feed forward-neural network (FNN) approach with finite memory neurons to model nonlinear transistor level buffers. After proper training, the FNN models can be cascaded with various channels characterized by either their geometrical or scattering parameters. At each cascading node, a FNN model is applied to predict the corresponding voltage waveform and forward that prediction along the link as input for the next available model. Compared to the industrial standard models like SPICE and IBIS, HSL simulation done through FNN models does not involve complicated converging iterations nor does it requires substantial domain knowledge. Furthermore, we demonstrated that by overlaying the high-correlation output responses from the FNN models, eye digram analysis can now be performed in a much faster manner as opposed to the conventional SPICE circuit solvers.

To Mom and Dad, who always believe in me and encourage me to go on every adventure. Here I am :)

## ACKNOWLEDGEMENT

This dissertation marks an important milestone in my life. I could not have imagined, on the day of 2012 when I joined University of Illinois at Urbana-Champaign as an undergrad, that I would be able to accomplish this much to earn the Doctoral degree. This long journey of academic pursuit and self-reflection would not been possible without the guidance from my dear advisor Professor José Schutt-Ainé, who introduced me to his group during my sophomore year. For ten years I have seen his students come and go, but what remains unchanged is his great passion towards scientific discovery as well as his continuous encouragement to all the group members. I am truly thankful for his patience and support throughout my course of study, especially during the time when I was in self-doubt.

Besides my advisor, I would like to express my deepest gratitude to the rest of my dissertation committee: Professor Jennifer Bernhard, Professor Erhan Kudeki and Professor Peter Dragic. I highly appreciate their valuable feedback to my preliminary exam presentation so that I was able to better improve my work before the final defense. It is my honor to have them witness my progress from an ignorant ECE freshman all the way till here.

Next, I would like to thank my colleagues who generously share their knowledge to lead me through the obstacles I encountered during my research. Dr. Thong Nguyen, whom I am forever grateful to, always patiently addresses my concerns even when they are naively dumb and time consuming to explain. I respect his attitudes towards academic-related matters: relentlessly searching for new break-through possibilities while selflessly devoting time to mentor students like me who are struggling. I wish to thank Dr. Hanzhi Ma as well for all the advice as a friend and collaboration as a researcher. It is frankly rare to meet a fellow female member in this field, yet I am so lucky to have her as both my roommate and co-author. I want to thank my group members: PhD candidate Bobi Shi, PhD candidate Juhitha Konduru, Dr. Xiao Ma, Dr. Xinying Wang, Dr. Xiou Ge, Gene Shiue and many who graduated before me. I dearly enjoy our talks and I hope for a bright future for all of you.

Also, I wisth to thank Karen Kuhns, Victor Shangguan, Dr. Hongliang Li, Dr. Shuo Liu and the rest of the residents on the fifth floor of ECEB. You constantly remind me that I am never fighting alone. I would also like to offer special thanks to Yuhe Cao, who, although no longer with us, continues to inspire me working towards this grand finale. I hope I had carried on your dream and may your soul rest in peace.

In addition, I want to express appreciation to my closest friends who motivate me through the unseen challenges. Many thanks to Siyan Guo, my lovely roommate for the past five years. We met during our freshman year and since then she has been looking out for me like a big sister. Although we parted after her graduation, our bound is stronger than ever when we encourage each other to purse our dreams. I would also like to thank my gaming buddies, Dr. Qing Ding and Jingchao Zhou. Time I spent in this little town is no longer tedious when we hop on discord and game for hours. This means a lot to me. I cannot imagine how stressful a PhD life can be without our happy hours in Overwatch. I thank Shuchen Song and G-Tay for their companions throughout my grad school journey. There were times when I deviated from the path, but they pulled me back and guided me all way till here.

Finally, my achievement today would not be possible without the support from my parents, Feng Zhao and Yan Liao. I deeply appreciate their unconditional love and encouragement, especially of their scarifies to send me eight thousands miles from home for better eduction. It is been too long since we last hold hands. I love you mom and dad. Although you will not be reading this dissertation, I still sincerely hope my work had done your proud.

# TABLE OF CONTENTS

| LIST OF FIGURES                                                                                                  |

|------------------------------------------------------------------------------------------------------------------|

| LIST OF TABLES                                                                                                   |

| CHAPTER 1 INTRODUCTION 1                                                                                         |

| 1.1 Overview                                                                                                     |

| 1.2       Review of Previous Works       4                                                                       |

| CHAPTER 2 MODELING TRANSCEIVER WITH FEED-FORWARD                                                                 |

|                                                                                                                  |

|                                                                                                                  |

|                                                                                                                  |

| 2.2 Memory Effect in Nonlinear System                                                                            |

| 2.3 Modeling Protocols                                                                                           |

| 2.4 Vector Fitting for Channel Parametrization                                                                   |

| 2.5 Construction of FNN Framework                                                                                |

| 2.6 Summary                                                                                                      |

| CHAPTER 3 APPLICATION OF FNN MODELS IN HIGH SPEED                                                                |

| LINK (HSL) SIMULATION                                                                                            |

| 3.1 Introduction $\ldots \ldots 24$ |

| 3.2 Trainig Environment                                                                                          |

| 3.3 HSL Configuration with NRZ Excitation                                                                        |

| 3.4 HSL Configuration with CTLE Equalization                                                                     |

| 3.5 HSL Configuration with Differential Signaling 40                                                             |

| 3.6 HSL Configuration with PAM-4 Excitation                                                                      |

| 3.7 Summary                                                                                                      |

|                                                                                                                  |

| CHAPTER 4 DISCUSSIONS                                                                                            |

| 4.1 Alternative Implementation                                                                                   |

| 4.2 Limitation $\ldots$ 56                                                                                       |

| CHAPTER 5 SUMMARY AND FUTURE WORK                                                                                |

| 5.1 Summary                                                                                                      |

| 5.1 Summary $\ldots$            |

| 0.2 FUDULE WOLK                                                                                                  |

| APPENDIX A AUTOMATION SCRIPT OF DATA TRANSFER- |          |

|------------------------------------------------|----------|

| RING BETWEEN ADS AND PYTHON                    | 72       |

| A.1 Batch Simulation                           | 72       |

| A.2 Reference Data Extraction                  | 74       |

| A.3 Eye Diagram                                | 75       |

|                                                |          |

| APPENDIX B CUDA TOOLKIT INSTALLATION AND USAGE |          |

|                                                |          |

| GUIDE FOR LINUX SYSTEM                         | 32       |

| B.1 CPU Only                                   | 82       |

|                                                | 82       |

| B.1 CPU Only                                   | 82<br>90 |

# LIST OF FIGURES

| $1.1 \\ 1.2 \\ 1.3$                                                         | Flowchart of a transient SPICE simulation Flowchart of a HSL simulation with IBIS-AMI models Modeling diagram of BNN, DNN and LVFNN on a HSL | 2<br>7<br>8                                        |

|-----------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| $2.1 \\ 2.2$                                                                | Comparison of workflow between SPICE/IBIS and FNN<br>Conversion between pole-residue model and its state-space                               | 9                                                  |

| 2.3                                                                         | form                                                                                                                                         | 15                                                 |

| 2.4                                                                         | three hidden layers and one output layer                                                                                                     | 17<br>19                                           |

| 2.5                                                                         | cost function $\mathcal{L} = \frac{1}{2}x^2$ using the derivatives                                                                           | 19<br>19                                           |

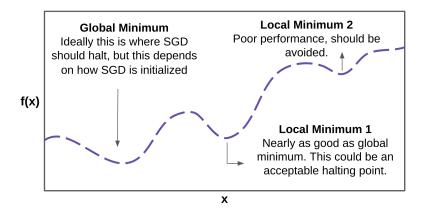

| 2.5<br>2.6                                                                  | Application of activation function $g$ in the hidden layers<br>Non-convex condition with multiple local minima                               | 19<br>20                                           |

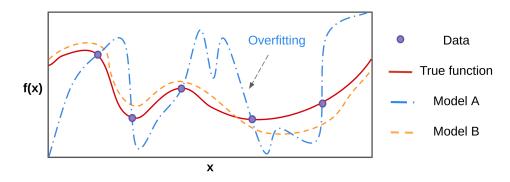

| $2.0 \\ 2.7$                                                                | Model A overfits the true function with low MSE.                                                                                             | 20<br>21                                           |

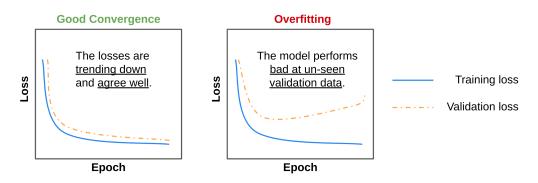

| 2.1                                                                         | Use validation data to prevent overfitting condition.                                                                                        | $\frac{21}{21}$                                    |

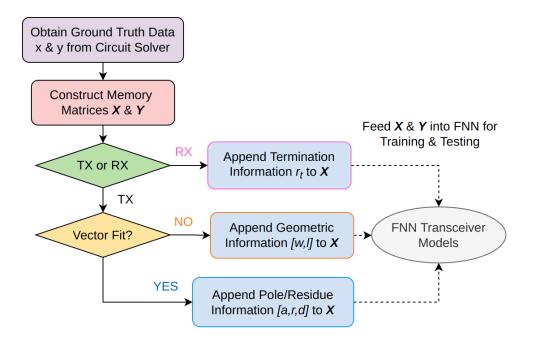

| 2.8<br>2.9                                                                  | FNN modeling workflow for the HSL transceivers.                                                                                              | $\frac{21}{22}$                                    |

| 2.9<br>2.10                                                                 | FNN structure for training TX with VF protocol.                                                                                              | $\frac{22}{22}$                                    |

|                                                                             |                                                                                                                                              |                                                    |

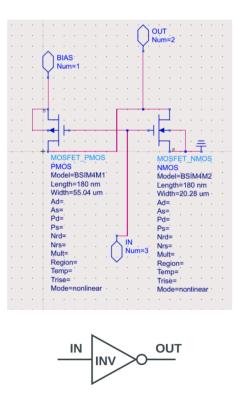

| 3.1<br>3.2<br>3.3                                                           | Transistor level circuit of CMOS inverter                                                                                                    | 25<br>25                                           |

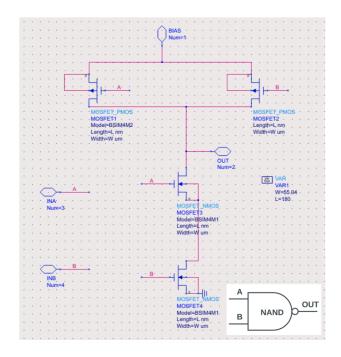

|                                                                             | Transistor level circuit of NAND gate                                                                                                        | 25                                                 |

| $3.2 \\ 3.3$                                                                | Transistor level circuit of NAND gate                                                                                                        |                                                    |

| 3.2<br>3.3<br>3.4                                                           | Transistor level circuit of NAND gate                                                                                                        | 25<br>26                                           |

| $3.2 \\ 3.3$                                                                | Transistor level circuit of NAND gate                                                                                                        | 25<br>26<br>26                                     |

| 3.2<br>3.3<br>3.4<br>3.5                                                    | Transistor level circuit of NAND gate                                                                                                        | 25<br>26<br>26<br>27                               |

| <ul> <li>3.2</li> <li>3.3</li> <li>3.4</li> <li>3.5</li> <li>3.6</li> </ul> | Transistor level circuit of NAND gate                                                                                                        | 25<br>26<br>26<br>27<br>28                         |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7                                      | Transistor level circuit of NAND gate                                                                                                        | 25<br>26<br>26<br>27<br>28<br>29                   |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                               | Transistor level circuit of NAND gate                                                                                                        | 25<br>26<br>26<br>27<br>28<br>29                   |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8                               | Transistor level circuit of NAND gate                                                                                                        | 25<br>26<br>27<br>28<br>29<br>29                   |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10                | Transistor level circuit of NAND gate                                                                                                        | 25<br>26<br>27<br>28<br>29<br>29<br>30             |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10                | Transistor level circuit of NAND gate                                                                                                        | 25<br>26<br>27<br>28<br>29<br>29<br>30             |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11        | Transistor level circuit of NAND gate                                                                                                        | 25<br>26<br>27<br>28<br>29<br>29<br>29<br>30<br>30 |

| 3.2<br>3.3<br>3.4<br>3.5<br>3.6<br>3.7<br>3.8<br>3.9<br>3.10<br>3.11        | Transistor level circuit of NAND gate                                                                                                        | 25<br>26<br>27<br>28<br>29<br>29<br>29<br>30<br>30 |

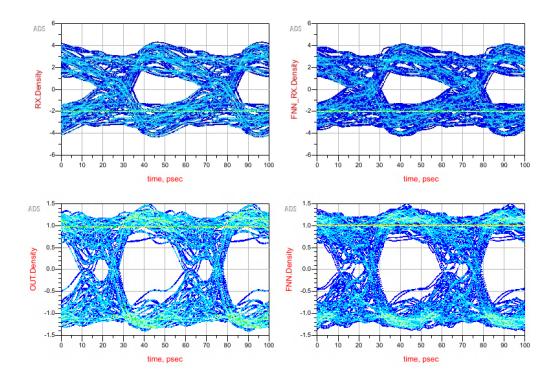

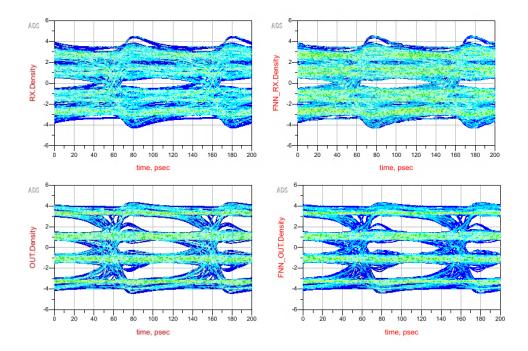

| 3.14 | Eye diagrams constructed by the reference and the FNN                                                                                             |    |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------|----|

|      | prediction                                                                                                                                        | 32 |

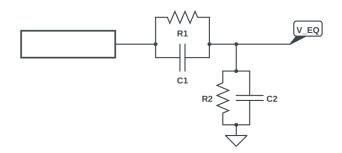

| 3.15 | High-pass RC circuit for passive CTLE                                                                                                             | 34 |

| 3.16 | Add CTLE to HSL: (a) Equalizer located in the intercon-                                                                                           |    |

|      | nect channel; (b) ADS scheamtic of a 10 Gbps HSL with                                                                                             |    |

|      | CTLE                                                                                                                                              | 35 |

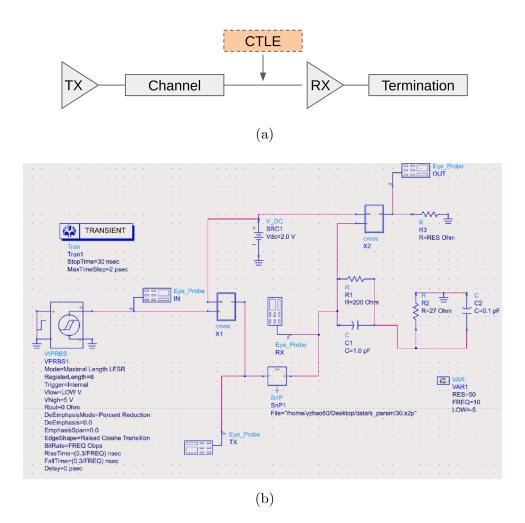

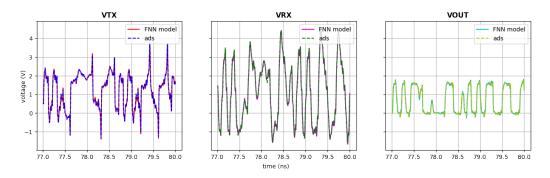

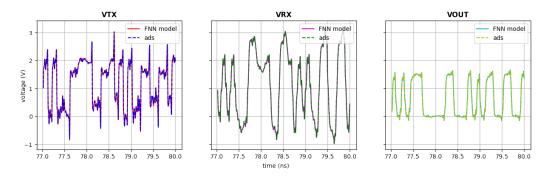

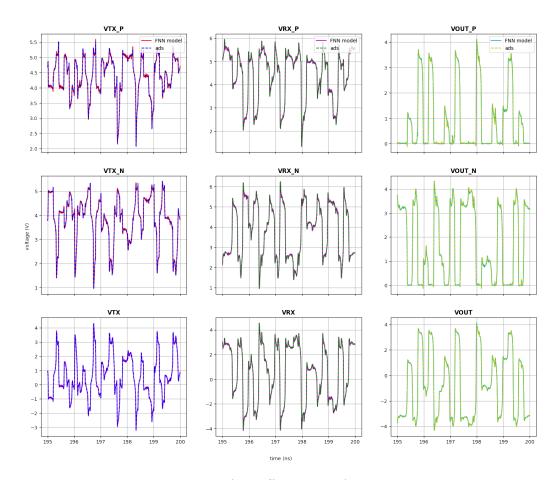

| 3.17 | FNN predictions of $V_{TX}$ , $V_{RX}$ and $V_{OUT}$ without CTLE                                                                                 | 38 |

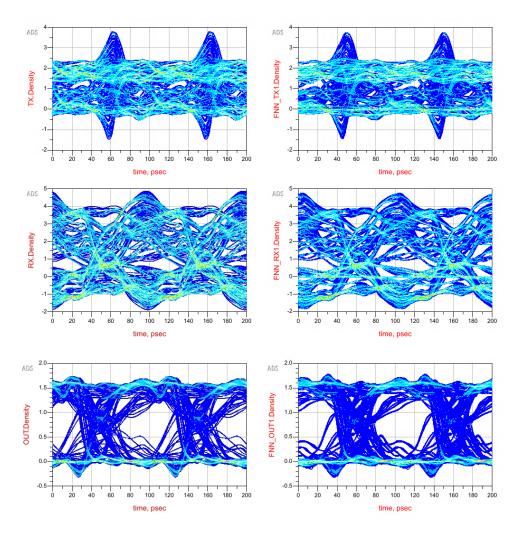

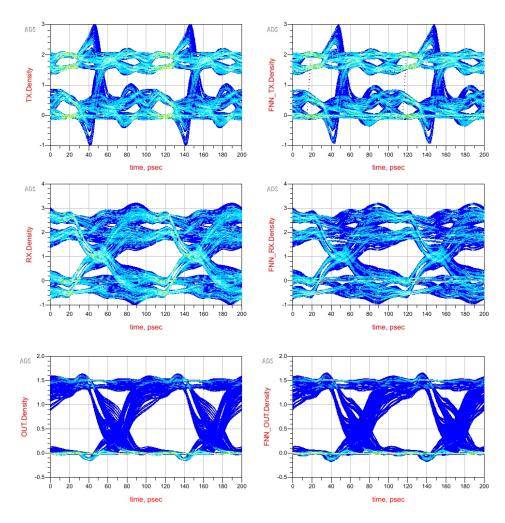

| 3.18 | Eye diagrams without CTLE. Left: ADS references. Right:                                                                                           |    |

|      | FNN predictions. Top to Bottom: $V_{TX}$ , $V_{RX}$ , $V_{OUT}$ .                                                                                 | 38 |

| 3.19 | FNN predictions of $V_{TX}$ , $V_{RX}$ and $V_{OUT}$ with CTLE                                                                                    | 39 |

|      | Eye diagrams with CTLE. Left: ADS references. Right:                                                                                              |    |

|      | FNN predictions. Top to Bottom: $V_{TX}$ , $V_{RX}$ , $V_{OUT}$ .                                                                                 | 39 |

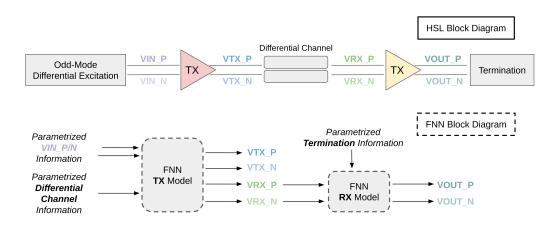

| 3.21 | The HSL and FNN block diagrams of transforming single-                                                                                            |    |

|      | ended signal to differential signals.                                                                                                             | 42 |

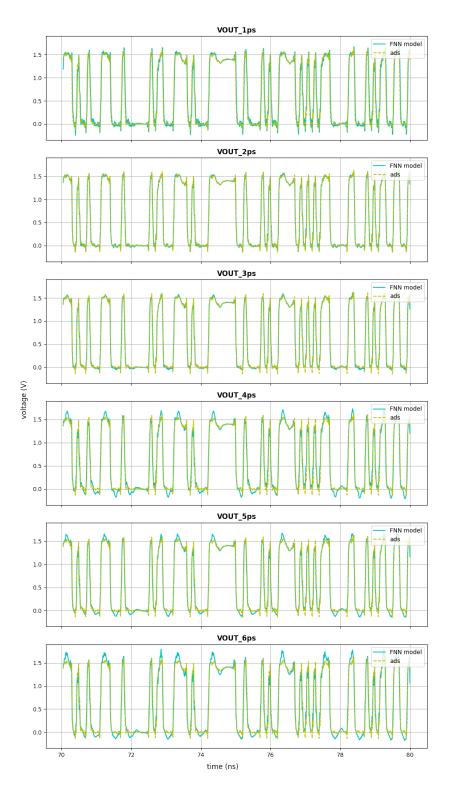

| 3.22 | FNN predictions for differential signaling test configuration.                                                                                    | 43 |

|      | FNN predictions for differential eyes at $V_{RX}$ and $V_{OUT}$ .                                                                                 |    |

|      | Left: ADS references. Right: FNN predictions. Top: $V_{RX}$ .                                                                                     |    |

|      | Bottom: $V_{OUT}$ .                                                                                                                               | 44 |

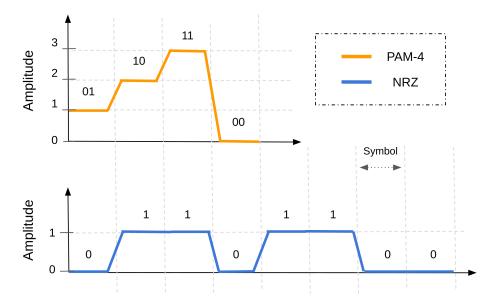

| 3.24 | Comparison of signal levels in NRZ and PAM-4 for the                                                                                              |    |

|      | same bits.                                                                                                                                        | 46 |

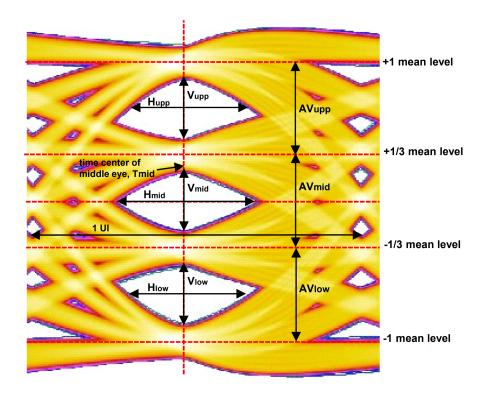

| 3.25 | PAM-4 eye parameters definition.                                                                                                                  | 46 |

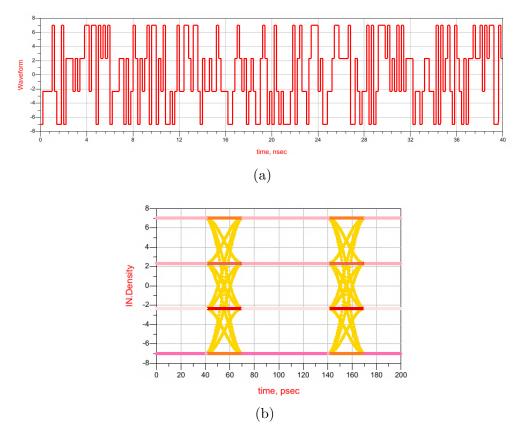

|      | Example of PAM-4 excitation: (a) A section of PAM-4                                                                                               | -  |

| 0.20 | source PRBS waveform; (b) Input's eye diagram.                                                                                                    | 47 |

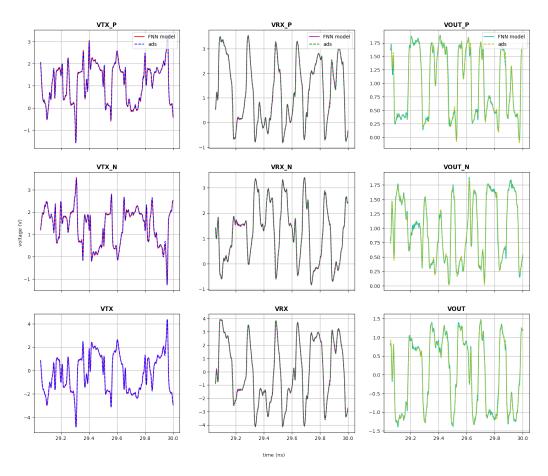

| 3.27 | FNN predictions for differential PAM-4 signaling test con-                                                                                        |    |

| 0.21 | figuration.                                                                                                                                       | 48 |

| 3.28 | FNN predictions for PAM-4 differential eyes at $V_{RX}$ and                                                                                       | 10 |

| 0.20 | $V_{OUT}$ . Left: ADS references. Right: FNN predictions.                                                                                         |    |

|      | Top: $V_{RX}$ . Bottom: $V_{OUT}$                                                                                                                 | 49 |

|      | $10p. r_{RX}. Dottom. r_{OU1}. \dots \dots$ | 10 |

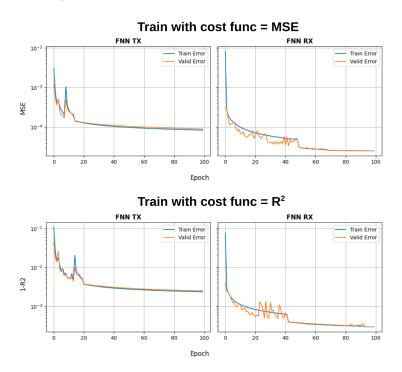

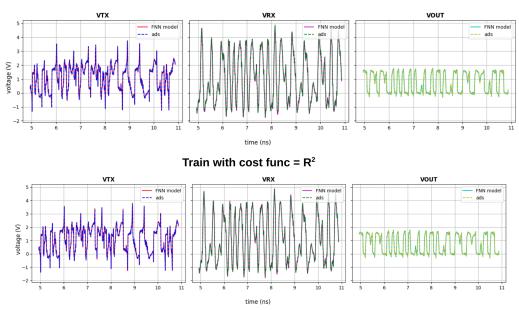

| 4.1  | Comparison of training convergences between the MSE and                                                                                           |    |

|      | $R^2$ loss functions                                                                                                                              | 53 |

| 4.2  | Comparison of predicted waveforms from MSE and $\mathbb{R}^2$                                                                                     |    |

|      | trained models.                                                                                                                                   | 54 |

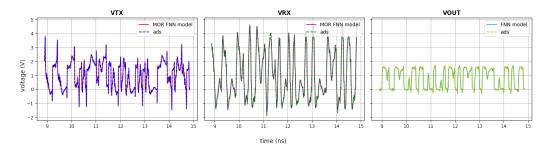

| 4.3  | Comparison of predicted waveforms from MOR FNN and ADS.                                                                                           | 56 |

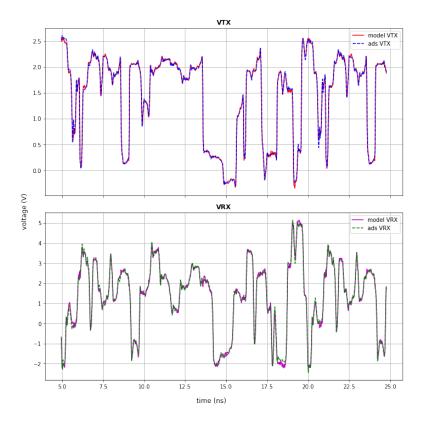

| 4.4  | FNN prediction of $V_{TX}$ and $V_RX$ for the interpolation test                                                                                  |    |

|      | on NAND TX.                                                                                                                                       | 58 |

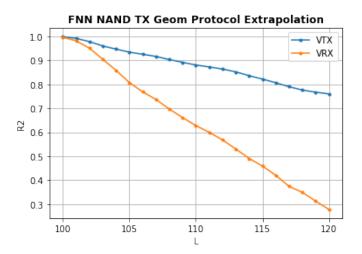

| 4.5  | $R^2$ scores of FNN prediction of $V_{TX}$ and $V_RX$ for the ex-                                                                                 |    |

|      | trapolation test on NAND TX.                                                                                                                      | 58 |

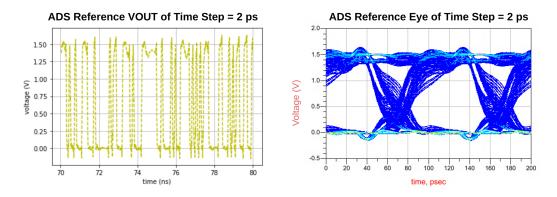

| 4.6  | ADS reference $V_{OUT}$ of time step sampled at 2 ps                                                                                              | 59 |

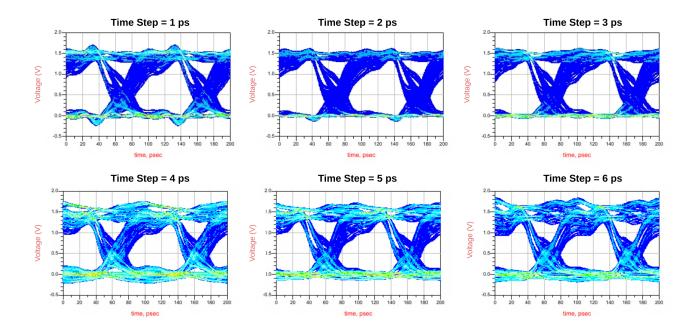

| 4.7  | FNN predicted $V_{OUT}$ eyes from different time step training                                                                                    | 60 |

| 4.8  | FNN predicted $V_{OUT}$ waveforms from different time step                                                                                        |    |

|      | training                                                                                                                                          | 61 |

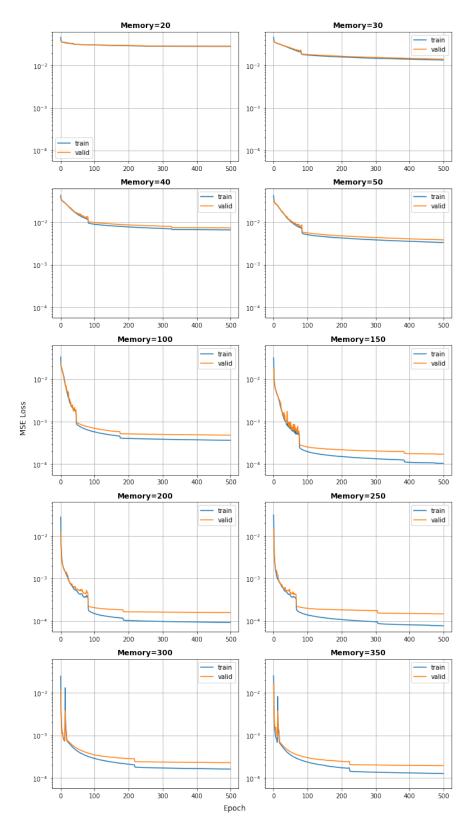

| 4.9  | Training and validation loss of FNN TX model with differ-                                                                                         |    |

|      | ent memory length.                                                                                                                                | 63 |

|      |                                                                                                                                                   |    |

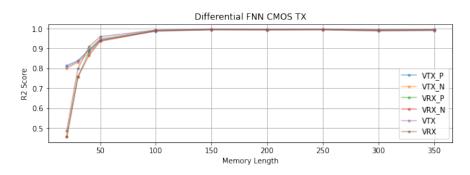

| 4.10 | Relation between modeling accuracy and memory length    | 64 |

|------|---------------------------------------------------------|----|

| 4.11 | FNN prediction of the inverter output when trained with |    |

|      | PRBS excitation.                                        | 65 |

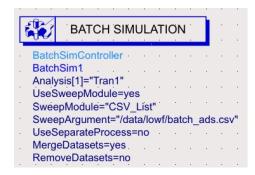

| A.1  | Batch simulation component in ADS                       | 72 |

| A.2  | Schematic for eye diagram comparison in ADS             | 77 |

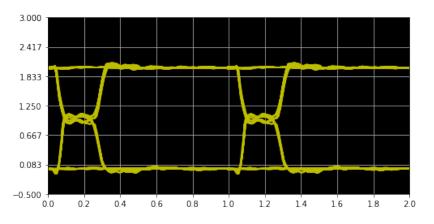

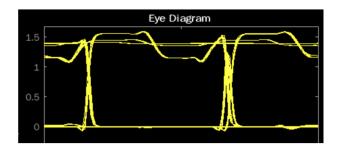

| A.3  | Example of eye diagram plotted with python              | 78 |

| A.4  | Example of eye diagram plotted with Matlab              | 79 |

| A.5  | Typical HSL eye diagram measurements                    | 80 |

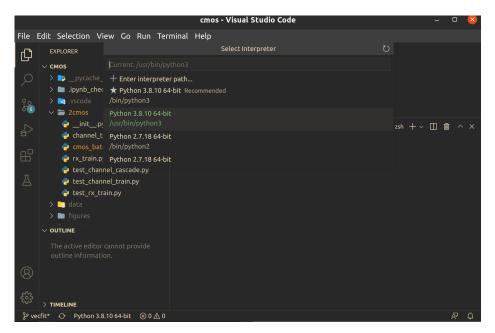

| B.1  | VS code installation                                    | 83 |

| B.2  | Launch VS code                                          | 84 |

| B.3  | VS code marketplace                                     | 85 |

| B.4  | Select Interpreter in VS code                           | 85 |

| B.5  | System processes interface                              | 87 |

| B.6  | Ubuntu additional driver setting (GPU)                  | 94 |

| B.7  | CUDA toolkit v11.3.0                                    | 95 |

| B.8  | Pytorch with CUDA 11.3 extension                        | 96 |

| B.9  | NVIDIA system management interface                      | 97 |

# LIST OF TABLES

| 1.1 | Simulated or measured elements required by the IBIS model .                                                   | 5  |

|-----|---------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Simulation or measurement environment of IBIS keywords                                                        | 6  |

| 3.1 | Range of sweeping values in ADS batch simulation                                                              | 27 |

| 3.2 | Comparison of eye diagram measurements                                                                        | 33 |

| 3.3 | Quantitative comparison of CTLE OFF eye diagrams in                                                           |    |

|     | Figure 3.18                                                                                                   | 40 |

| 3.4 | Quantitative comparison of CTLE ON eye diagrams in Fig-                                                       |    |

|     | ure 3.20                                                                                                      | 40 |

| 3.5 | Precentage error between reference and FNN for eye dia-                                                       |    |

|     | grams in Figure 3.18 and Figure 3.20                                                                          | 40 |

| 3.6 | $R^2$ scores for FNN predicted differential waveforms                                                         | 43 |

| 3.7 | Quantitative comparison of differential eye diagrams                                                          | 45 |

| 3.8 | Quantitative comparison of PAM-4 differential eye diagrams $% \left( {{{\rm{A}}} \right)_{\rm{A}}} \right)$ . | 50 |

| 4.1 | Eye diagram measurement of FNN CMOS RX model trained                                                          |    |

|     | with time step $(Tstep) = [1, 2, 3, 4, 5, 6]$ ps                                                              | 60 |

# CHAPTER 1 INTRODUCTION

### 1.1 Overview

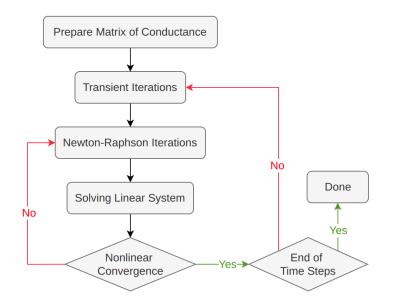

Due to the ever increasing demand of parallel processing and multi-level cache memory, integrated circuit (IC) designers nowdays are fitting billions of 7 nm technology transistors on a fingernail-size chip [1]. While the transistor count keeps growing at the rate of Moore's law, on-chip signal integrity (SI) analysis has never been more challenging given the accumulating IC complexity. The burden not only lies in the number of the gates, but also the shrank timing and noise margin that are outcomes of the faster transition times [2]. Conventionally, SI engineers use Simulation Program with Integrated Circuit Emphasis (SPICE) for time domain simulation by solving for node voltage and branch current at each time step. Nevertheless, this process becomes extremely computationally expensive when it comes to transient simulation, where nonlinearities are taken into account. As shown in Fig. 1.1, multiple Newton-Raphson iterations are required before convergence is achieved at every time step for a nonlinear system. Given the super-linearity of the computation size, it is impractical to apply SPICE for large scale SI validation if structural models of transistors are used.

To improve the analysis efficiency, behavioral models are introduced as black-box alternatives to their equivalent SPICE-like circuits. Instead of accessing the transistor level design, the model yields the output in response to the excitation based on either previously simulated data or bench measurements. One of the most well-known standards is the I/O Buffer Information Specification (IBIS) model, where the I/O's voltage and current data are saved as tables categorized by various usage scenarios [4]. With a slight decrease in accuracy, much faster simulation speed is attained in the absence

Figure 1.1: Flowchart of a transient SPICE simulation [3].

of nonlinear solving iterations. While IBIS models are supported by the vast majority of IC vendors because of their intellectual property (IP) protection nature, end users are assumed to have substantial domain knowledge in order to use the models properly in addition to producing them. As the IBIS standard evolves over time to include more complicated features like interconnect and algorithmic calculation [5], the learning curve faced by a novice user is becoming excessively steep.

In the effort of simplifying the modeling process, attempts were made deriving behavior models with machine learning (ML) methods. Rather than physically mimicking the SPICE circuit with current sources and passive components [6], the ML approach approximates the nonlinear function represented by the I/O data through training and stores the vector of kernels as the model. In recent years, many remarkable results are reported on modeling highly nonlinear electronic devices and systems with supervised learning algorithm, to be specific, the neural network (NN) framework. For instance, several research efforts successfully model broadband power amplifiers with variants of NN, including convolutional neural network (CNN) [7], deep neural network (DNN) [8] and memory polynomial neural network (MPNN) [9]. There are also articles that focus on modeling sequential circuits for digital designs simulation with recurrent neural network (RNN) [10, 11, 12]. Nevertheless, very few NN based behavior models were developed that are suitable for the high speed link (HSL) simulation (see Chapter 1.2.2). To perform such analysis, a passive channel is placed in-between the nonlinear transceiver models and millions of bits of data is collected at the cascading nodes to construct eye diagrams which are used to assess the link performance. The major issue with the reported NN frameworks is the ambiguous statement on the cascade-ability of the transmitter(TX) and the receiver (RX) blocks. In other words, the existing modeling techniques treated a particular configuration of HSL as an entity with an underlaying assumption that the transceiver model needs to be re-trained every time when a new channel is presented. Since the required training time of the NN models is as much, if not more, than performing the SPICE nonlinear iterations, the purpose of adopting behavior models in HSL simulation is defeated unless the cascade-ability of the transceiver models is properly addressed.

To resolve the aforementioned issue, this dissertation proposed a feedforward neural network (FNN) based modeling technique for generating cascadeable transceiver blocks that are dedicated for HSL analysis. Different protocols are assigned to the TX and RX models to ensure the trained blocks could function independently regardless of changes in channel. In terms of cascading, the FNN RX model always takes the voltage predictions from the previous block as input and then pass on the calculated responses to the next available block along the link. It is also worth noting that when applying the FNN models, computation efficiency and convergence are guaranteed because the HSL simulation is now merely done by matrix multiplication between the voltage excitations and the kernels stored within the TX/RX models. The performance of this new method is examined by comparing the runtime and waveforms between the FNN model and the SPICE circuit for many distinct test cases, namely the NRZ excitation, PAM-4 excitation, DFE equalization and differential signaling.

This dissertation is structured as follows: In Chapter 1, the motivation of this project and a review on the related previous works are presented. Chapter 2 explained the TX/RX modeling protocols and the structure of FNN. Then in Chapter 3, training procedure of the two transistor-level gate examples, NAND and CMOS, are demonstrated and the trained blocks are cascaded with testing channels. The accuracy of the modeling results are evaluated against their references from a commercial circuit solver as well in this chapter. The proposed method's limitation and alternative implementation are discussed in Chapter 4. Chapter 5 summarizes the contribution of the proposed approach and provides an outlook on future developments. At last, there are two appendixes that explain the training data preparation and hardware acceleration with CUDA in detail.

## 1.2 Review of Previous Works

This section discusses the currently available behavioral modeling techniques for HSL simulation. The first subsection focus on the traditional IBIS approach, which is the golden standard adopted by many EDA tool. The second subsection focus on the more recent NN based methods, of which the modeling accuracy is justified but are greatly limited by their incapability of functioning in a cascade-able manner.

#### 1.2.1 IBIS and IBIS-AMI Models

As a global industry standard, IBIS and IBIS-AMI models offer good accuracy in nonlinear system simulation as well as protecting vendors intellectual property. Begin from early 1990s, semiconductor companies started supplying IBIS models to their end users to simulate SI at chip and board level. This modeling technique is particularly well suited for large scale analysis because the device's I/O relation is pre-solved on the vendor side under typical, maximum and minimum operation conditions. The enhanced version of IBIS, called the IBIS-AMI with BIRD flow, was first released in 2012 aiming to specify the interface between the TX/RX and the channel simulator. In this subsection, a brief introduction of both models is given so the readers understand how IBIS functions as a cascade-able unit in HSL simulation.

The IBIS model is a human-readable text file (\*.ibis) that records the buffer's I-V (current versus voltage) and switching characteristics V-T (output voltage versus time) in a tabular format [14]. In addition, it also allows

| Keyword            | Type | I/O buffer | Input buffer | Output buffer |

|--------------------|------|------------|--------------|---------------|

| [GND Clamp]        | I-V  | Yes        | Yes          | No            |

| [POWER clamp]      | I-V  | Yes        | Yes          | No            |

| [Pullup]           | I-V  | Yes        | No           | Yes           |

| [Pulldown]         | I-V  | Yes        | No           | Yes           |

| [Rising Waveform]  | V-T  | Yes        | No           | Yes           |

| [Falling Waveform] | V-T  | Yes        | No           | Yes           |

Table 1.1: Simulated or measured elements required by the IBIS model

the simulator to take in account the information of the packaging around the buffer such as the parasitic RLC, which are stored as optional lines in electrical parameter keywords. In its simplest format, IBIS model characterize the buffers with six sets of I-V and V-T data as shown in Table 1.1. Each of the keywords is a look-up table simulated or measured with the steps described in Table 1.2. Generally, the min-corner case is generated with the weakest driver strength and/or slowest bit rate while the max-corner case takes the reverse. The exact values of  $V_{SS}$  and  $V_{DD}$  are determined by the realistic use cases of the buffer. For example, a CMOS can be modeled with  $V_{SS}$ equals to ground and  $V_{DD}$  equals to its biasing voltage. For more complicate designs like differential buffer, additional keywords such as differential capacitance are required to fully characterize the device. After generating an IBIS model, one must manually validate that the extracted I-V and V-T tables are in accordance with the SPICE simulation result as well as their compliance with the IBIS syntax. In the context of a transient simulation, the solver first calculates the dependent multipliers Ku(t) and Kd(t) from the V-T tables and then perform a summation of the currents gathered at the output node as

$$-Iout(t) = Ku(t) \cdot Ipu(V) + Kd(t) \cdot Ipd(V) + Ipc(V) + Igc(V), \quad (1.1)$$

where the Ix(V) values are determined according to the IV tables at each time point using piecewise linear interpolation [15]. Overall, as long as the range of IV/VT tables covers the voltage excitation used in the transient simulation, IBIS model is theoretically capable of a yielding accurate results for a cascading chain of any length.

| Keywords           | Data extraction flow (typical and min/max-corners)                                                                                                                                                                                                                                                                                                                                                     |

|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| [GND Clamp]        | Disable the output pin and connect it to a ground ref-<br>erence or pull down reference $-V_{SS}$ . Insert a dc volt-<br>age source $V_{pin}$ in-between the connection and perform a<br>sweep from $-(2 \times V_{SS} + V_{DD})$ to $(2 \times V_{DD} + V_{SS})$ . Measure<br>the current $I_{pin}$ at the output. Gather values of $I_{pin}$ and<br>$V_{pin}$ to make the I-V table.                 |

| [POWER clamp]      | Disable the output pin and connect it to a power/pull-up reference $V_{DD}$ . Insert a dc voltage source $V_{pin}$ in-between the connection and perform a sweep from $-(2 \times V_{SS} + V_{DD})$ to $(2 \times V_{DD} + V_{SS})$ . Measure the current $I_{pin}$ at the output. Gather values of $I_{pin}$ and $V_{pin}$ to make the I-V table.                                                     |

| [Pullup]           | Enable the output pin and set it to logic high. Connect<br>it to a power/pull-up reference $V_{DD}$ . Insert a dc volt-<br>age source $V_{pin}$ in-between the connection and perform a<br>sweep from $-(2 \times V_{SS} + V_{DD})$ to $(2 \times V_{DD} + V_{SS})$ . Measure<br>the current $I_{pin}$ at the output. Gather values of $I_{pin}$ and<br>$V_{pin}$ to make the I-V table.               |

| [Pulldown]         | Enable the output pin and set it to logic low. Connect it<br>to a ground reference or pull down reference $-V_{SS}$ . Insert<br>a dc voltage source $V_{pin}$ in-between the connection and<br>perform a sweep from $-(2 \times V_{SS} + V_{DD})$ to $(2 \times V_{DD} + V_{SS})$ .<br>Measure the current $I_{pin}$ at the output. Gather values of<br>$I_{pin}$ and $V_{pin}$ to make the I-V table. |

| [Rising Waveform]  | Enable the output pin and apply appropriate input volt-<br>age pulse so its logic state switches from low to high. In-<br>sert a fixture of $r \ \Omega$ between the pin and the power/pull-<br>up reference $V_{DD}$ . Measure the rising slew rate $dV/dt$ and<br>record it as the V-T table.                                                                                                        |

| [Falling Waveform] | Enable the output pin and apply appropriate input volt-<br>age pulse so its logic state switches from high to low. In-<br>sert a fixture of $r \ \Omega$ between the pin and the pull down<br>reference $-V_{SS}$ . Measure the falling slew rate $dV/dt$ and<br>record it as the V-T table.                                                                                                           |

Table 1.2: Simulation or measurement environment of IBIS keywords [13]

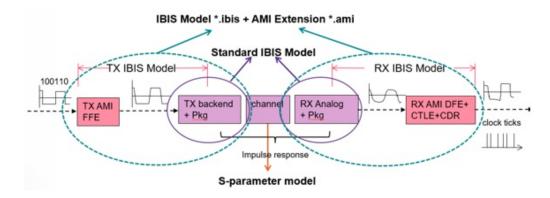

Figure 1.2: Flowchart of a HSL simulation with IBIS-AMI models [16].

The IBIS-AMI model is invented to standardize the HSL simulation with IBIS specifications. The model is divided into two files: the analog IBIS part (\*.ibis) and the executable algorithmic AMI part (\*.dll). As shown in Figure 1.2, the equalization settings such as FFE in TX and DFE in RX are included in the AMI extension file. The HSL transient simulation with IBIS-AMI models begins with the calculation of impulse response, which is a combined force of Equation (1.1) along with applying the inverse Fourier transform on the S-parameter characterized channel. Then, the AMI portion acts as a DSP block which takes the calculated impulse response and produces a modified output based on the equalization presets. It is worth mentioning that if the TX/RX IBIS-AMI models in the HSL support the same link training protocol, the new versions of AMI could perform dynamic equalization, meaning that the tap values in DFE are adaptive to the signature of the channel. Note that if IBIS-AMI models are used, the HSL is strictly defined as one TX cascading with one channel and one RX, which is not as robust as the previously mentioned IBIS model.

#### 1.2.2 Neural Network Models

To facilitate the process of generating and utilizing customizable behavior models in HSL simulation, NN based modeling techniques are being explored recently, taking advantage of the hardware acceleration for faster convergence during the training phase. For instance, Chu *et al.* [17] introduced a back propagation based NN (BNN) model that predicts the output after the receiver (RX) given the excitation before the transmitter (TX). This work

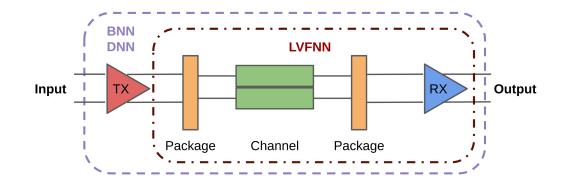

Figure 1.3: Modeling diagram of BNN, DNN and LVFNN on a HSL.

proofs that the NN could handle nonlinear behaviors (e.g. mismatch between the rising and falling time in the excitation) well with only three hidden layers. Similarly, Lu *et al.* [18] adopted a DNN model that accurately predicts the eye height at RX with variations in the channel geometry and TX/RX jitters. Another example is the Laguerre–Volterra feed-forward neural network (LVFNN) suggested by Wang *et al.* [19]. This work focus on reducing the required size of NN when modeling a nonlinear RX component with PAM-4 excitation. While all the above papers suggested a good correlation between the modeling results and SPICE references, the modeling techniques they demonstrated is performed on the entire HSL instead of a single TX or RX component as shown in Figure 1.3. Since the reported techniques use a single, large NN to model the entire link, they are oftentimes not robust enough for a real design scenario: A new transceiver model is required every time when HSL composition changes.

## CHAPTER 2

# MODELING TRANSCEIVER WITH FEED-FORWARD NEURAL NETWORK (FNN)

#### 2.1 Introduction

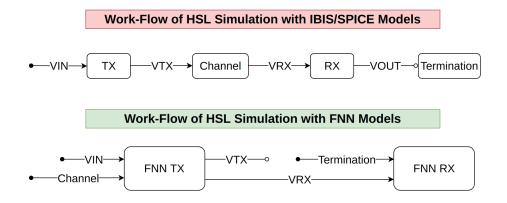

In this Chapter, the methodology of developing cascade-able transceiver models with feed-forward neural network (FNN) is presented. As shown in Figure 2.1, the FNN transceiver models will be cascaded to perform HSL simulation with a slightly different work-flow compared to the traditional IBIS/SPICE models. This modification is mandatory because the TX/RX FNN models are expected to be resilient to certain variations in the cascading chain and hence, requiring the parameterized channel and termination information as inputs. In addition, it is worth noting that modeling with FNN creates a self-sustain system, where its HSL analysis no longer demands any commercial EDA tool: The simulation is now done through a chain of matrix multiplication based on the stored kernels in the TX/RX FNN models. Thanks to the model's cascade-bility, one could also use a single block of FNN model independently to test the buffer's performance.

Figure 2.1: Comparison of workflow between SPICE/IBIS and FNN.

## 2.2 Memory Effect in Nonlinear System

Given that the transceivers nowadays are generally nonlinear devices, the HSL system they form is considered to possess *memory* of which the discrete output y(n) depends on both the current and the past states of the input x(n). This nonlinear, causal, stable, time-invariant system is typically described by the truncated Volterra series [20]

$$y(n) = h_0 + \sum_{\tau_1=0}^{M} \sum_{\tau_2=\tau_1}^{M} \dots \sum_{\tau_p=\tau_{p-1}}^{M} h_p(\tau_1,\dots,\tau_p) \prod_{j=1}^{p} x(n-\tau_j), \qquad (2.1)$$

where M is the memory length and p is the pth-order of the Volterra kernel (VK). Although mathematically all the VKs can be estimated by solving a least-mean-square (LMS) equation, the problem soon becomes intractable because the number of VKs to be solved is a exponential function in respect to p and M.

To lift the curse of dimensionality, many tend to apply the discrete Laguerre function as the projecting basis for VKs expansion [21]. Such function can be expressed as

$$\phi_r(\tau) = \alpha^{\frac{\tau-r}{2}} (1-\alpha)^{\frac{1}{2}} \sum_{k=0}^r (-1)^k \begin{pmatrix} \tau \\ k \end{pmatrix} \begin{pmatrix} r \\ k \end{pmatrix} \alpha^{r-k} (1-\alpha)^k$$

(2.2)

with  $\phi_r(t)$  being the *r*-th orthonormal basis function. From there, the VKs can now be expanded as

$$h_{0} = \theta_{0}$$

$$h_{1}(\tau) = \sum_{r=1}^{r=R} \theta_{r} \phi_{r}(\tau)$$

$$h_{2}(\tau_{1}, \tau_{2}) = \sum_{r_{1}=1}^{r_{1}=R} \sum_{r_{2}=1}^{r_{2}=R} \theta_{r_{1}, r_{2}} \phi_{r_{1}}(\tau_{1}) \phi_{r_{2}}(\tau_{2})$$

$$h_{p}(\tau_{1}, \dots, \tau_{p}) = \sum_{r_{1}=1}^{r_{1}=R} \dots \sum_{r_{n}=1}^{r_{n}=R} \theta_{r_{1}, \dots, r_{n}} \prod_{l=1}^{p} \phi_{l}(\tau_{l}),$$

(2.3)

where R is the max order of the Laguerre function. After denoting a function  $\ell$  of all known parameters as

$$\ell_r = \sum_{\tau=0}^{M} \phi_r(\tau) x(n-\tau),$$

(2.4)

Equation (2.1) can be transformed to

$$y(n) = \theta_0 + \sum_{r=1}^R \theta_r \ell_r + \sum_{r_1=1}^{r_1=R} \sum_{r_2=1}^{r_2=R} \theta_{r_1,r_2} \ell_{r_1} \ell_{r_2} + \dots + \sum_{r_1=1}^{r_1=R} \dots \sum_{r_n=1}^{r_n=R} \theta_{r_1,\dots,r_n} \prod_{i=1}^p \ell_{r_i}.$$

(2.5)

with  $[\theta_0, \theta_{r1}, \dots, \theta_{rn}]$  being the new kernels. Given that R is usually a much smaller number than T, the identification of the kernels is thereby greatly simplified [19, Tab. I, II].

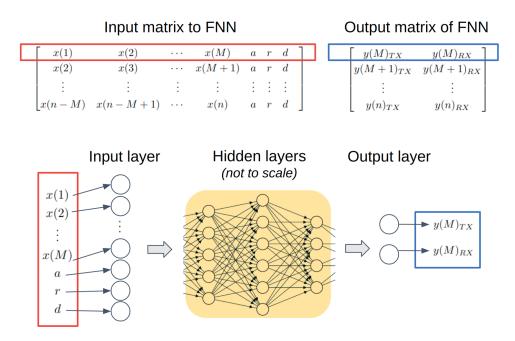

However, this approach is problematic when x(n) is a long sequence sampled at tiny time steps. Even with a relatively small R, at a certain point, convolution between matrices  $\phi_r$ ,  $\theta_r$ , and x(n) may exceed the available computation capability. In other words, to completely avoid the convolutions in Equation (2.1), the nonlinearity of the system should be addressed not as a summation but a nonlinear function f such that for a input memory matrix  $\boldsymbol{X}$  of size  $(n - M) \times M$ , the I/O relation between  $\boldsymbol{X}$  and the output  $\boldsymbol{Y}$  can be written in the form:

$$\boldsymbol{X} = \begin{bmatrix} x(1) & x(2) & \cdots & x(M) \\ x(2) & x(3) & \cdots & x(M+1) \\ \vdots & \vdots & \vdots & \vdots \\ x(n-M) & x(n-M+1) & \cdots & x(n) \end{bmatrix}$$

(2.6)

$$\boldsymbol{Y} = \begin{bmatrix} y(M) & y(M+1) & \cdots & y(n) \end{bmatrix}^T = f(\boldsymbol{X}).$$

(2.7)

As demonstrated in the later sections, the exact implementation of f is determined by the structure of the hidden layers in the FNN. The bottom line is f does not necessarily take the same form for all buffers, meaning that it is up to the designers to decide if more nonlinearity should be added into f by adjusting the FNN framework.

## 2.3 Modeling Protocols

Besides the memory sequences, the FNN model demands information of the channel as well as the load condition in order to execute a comprehensive HSL simulation. These extra data are referred to *protocol* in this section. Protocols are appended to every row of the input memory matrix such that the FNN recognizes different configurations of HSL. Conceptually speaking, there is no fixed protocol because as long as the modeling and application use the same terms, FNN models could yield accurate prediction correspondingly. The TX/RX protocols described below are merely a proof of concept and are subject to future expansion for more advanced HSL usage.

Since the TX model is expected to make voltage predictions for both before and after the channel, two protocols are proposed on how the channel is parameterized and incorporated into the framework of the model:

- 1. For channels that are uniform and homogeneous (e.g., a section of microstrip line (MLIN)), use their geometric features such as width w, length l, dielectric constant  $\epsilon_r$ , etc.

- 2. For more complexly structured channel, use the terminal frequency response such as the S-parameter.

The geometric approach is straightforward and already proofed to be NNcompatible for eye height and width prediction [22]. Meanwhile, the Sparameter approach permits a wider application given that most of the channels in HSL simulations are inhomogeneous. Both protocols are demonstrated in Chapter 3 to show that accuracy-wise, there is essentially no difference in using either of them.

Meanwhile, the load condition is specified in the RX protocol. As a proof of concept attempt, a resistor of  $r_t \Omega$  is used to terminate the HSL. This assumption can be easily expanded to include more components such as capacitors and inductors by adjusting the RX protocol. Overall, the concept of protocol is very similar to the  $V_{DD}$  and  $V_{SS}$  sweep in the IBIS model: The range of the sweeping values adopted by the protocol determines the model's operation limitation.

## 2.4 Vector Fitting for Channel Parametrization

Vector fitting (VF) is a black-box modeling technique that extracts reducedorder passive macromodel from measured or computed frequency domain data with rational function approximations [23]. Compared to the traditional approximation function in Equation (2.8) where the unknown coefficients  $a_n$ and  $b_n$  are binded with different powers of s, VF scales the function with respect to a single column of s and reduce the approximation to a linear problem that allows higher order terms for fitting over a wide frequency range.

$$F(s) \approx \frac{a_0 + a_1 s + a_2 s^2 + \ldots + a_N s^N}{b_0 + b_1 s + b_2 s^2 + \ldots + b_N s^N}$$

(2.8)

Given a symmetric *n*-port S-parameter matrix S sampled as a function of frequency  $s = j\omega$ , the rational approximation function used by VF can be represented by

$$\boldsymbol{S}(s) = \sum_{m=1}^{N} \frac{\boldsymbol{r}_m}{s - a_m} + \boldsymbol{d}, \qquad (2.9)$$

where  $a \in \mathbb{C}^N$  denotes the complex pole,  $\mathbf{r} \in \mathbb{C}^{n \times n \times N}$  is the complex residue,  $\mathbf{d} \in \mathbb{R}^{n \times n}$  is the real constant and N is the number of poles required for a good fit of  $\mathbf{S}(s)$  which depends on the shape of the responses. The approximation begins with pole identification by solving a least square (LS) linear problem in Equation (2.10), where a set of starting poles  $\{q_m\}$  are used to launch the re-location process in Equations (2.11) and (2.12).

$$\sigma(s)\boldsymbol{S}(s) = p(s) \tag{2.10}$$

$$\sigma(s) = \sum_{m=1}^{N} \frac{\tilde{\boldsymbol{r}}_m}{s - q_m} + 1 \tag{2.11}$$

$$p(s) = \sum_{m=1}^{N} \frac{\boldsymbol{r}_m}{s - q_m} + \boldsymbol{d}$$

(2.12)

As explained in [24], the poles of S(s) are identical to the zeros of  $\sigma(s)$ ,

which can be obtained as

$$\{a_m\} = \operatorname{eig}\left(\boldsymbol{Q} - \boldsymbol{b} \cdot \boldsymbol{c}^T\right), \qquad (2.13)$$

where Q is a diagonal matrix consists of  $q_m$ , b is a column vector filled with ones, and  $c^T$  is a row vector made of residues  $\tilde{r}_m$ . The initial choices of  $\{q_m\}$ are generally complex conjugate pairs because the purely real poles might cause Equation (2.13) to be ill-conditioned. Note that Equations (2.10)-(2.13) can be carried out iteratively with the new poles  $\{a_m\}$  substituting the previous ones  $\{q_m\}$  for more precise fitting. When unstable poles are encountered, VF inverts the sign of their real part to ensure overall stability.

Moreover, Gustavsen [25] improved the LS convergence by replacing Equation (2.11) with Equation (2.14) and Equation (2.13) with Equation (2.15). This allows a more relaxed fitting because the previous method is normalized by a unity term that forces  $\sigma(s) = 1$  at high frequency. An additional normalization function is introduced as shown in Equation (2.16) where  $N_s$  is the number of frequency points in  $\mathbf{S}(s)$ . After the elimination of the asymptotic requirement in Equation (2.10),  $\sigma(s)$  can now theoretically approach a much smaller value at infinite frequency. With the poles being identified, Equation (2.10) can be transformed to another LS equation where  $\mathbf{r}$  and  $\mathbf{d}$ are solved [23, eq. (A.1)-(A.8)].

$$\sigma(s) = \sum_{m=1}^{N} \frac{\tilde{\boldsymbol{r}}_m}{s - q_m} + \tilde{\boldsymbol{d}}$$

(2.14)

$$\{a_m\} = \operatorname{eig}\left(\boldsymbol{Q} - \boldsymbol{b} \cdot \tilde{\boldsymbol{d}}^{-1} \cdot \boldsymbol{c}^T\right)$$

(2.15)

$$\operatorname{Re}\left\{\sum_{k=1}^{N_s} \left(\sum_{m=1}^N \frac{\tilde{\boldsymbol{r}}_m}{s_k - a_m} + \tilde{\boldsymbol{d}}\right)\right\} = N_s$$

(2.16)

Although VF always yields guaranteed stable poles, the passivity of the pole-residue model is not yet examined in the previous procedures. Thus, a further tuning step with Hamiltonian matrix [26] is performed on the state-space representation of the model. Since S-parameter is only suppose to characterize a passive system, S(s) is analytic on the open right half plane

[27] and should be bounded by unity:

$$\left(\boldsymbol{I} - \boldsymbol{S}(s)^{H} \boldsymbol{S}(s)\right) > 0, \qquad (2.17)$$

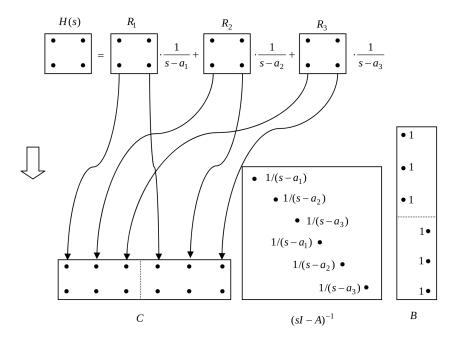

where H denotes the conjugate transpose (Hermitian) operation and I is the unity matrix. Then, the pole-residue model is transformed to its statespace form in Equation (2.18) by seeking similar terms in Equation (2.10). With the extraction steps explained in [28], the state variables are listed in Equation (2.19) where  $A_M$  is constructed by concatenating the scalar  $a_m$ diagonally. The dimensions of the matrices A, B, C and D are  $nN \times nN$ ,  $nN \times n$ ,  $n \times nN$  and  $n \times n$  respectively. Figure 2.2 illustrates an example of the transformation from pole-residue model to its state-space representation where number of ports n = 2 and max order of poles N = 3.

$$S(\omega) = C(j\omega I - A)^{-1}B + D$$

$$A = diag[A_1, A_2, \dots, A_M]$$

$$B = [I, I, \dots, I]$$

$$C = [r_1, r_2, \dots, r_m]^T$$

$$D = d$$

$$(2.18)$$

Figure 2.2: Conversion between pole-residue model and its state-space form.

From there, passivity assessment can be completed by evaluating the eigenvalues  $\lambda$  of the Hamiltonian matrix as

$$\boldsymbol{H} = \begin{bmatrix} \boldsymbol{A} - \boldsymbol{B}\hat{\boldsymbol{R}}^{-1}\boldsymbol{D}^{T}\boldsymbol{C} & -\boldsymbol{B}\hat{\boldsymbol{R}}^{-1}\boldsymbol{B}^{T} \\ \boldsymbol{C}^{T}\hat{\boldsymbol{S}}^{-1}\boldsymbol{C} & -\boldsymbol{A}^{T} + \boldsymbol{C}^{T}\boldsymbol{D}\hat{\boldsymbol{R}}^{-1}\boldsymbol{B}^{T} \end{bmatrix}, \qquad (2.20)$$

where  $\hat{\boldsymbol{S}} = (\boldsymbol{D}\boldsymbol{D}^T - \boldsymbol{I})$  and  $\hat{\boldsymbol{R}} = (\boldsymbol{D}^T\boldsymbol{D} - \boldsymbol{I})$ . Violations are checked at any imaginary part of  $\lambda$  that defines a crossover frequency js where a singular value touches the unity threshold [29]. Faster singularity analysis, as indicated in [30] and [31], can be achieved by reducing the size of  $\boldsymbol{H}$  based on the symmetries in the S-parameter. A symmetric state-space model is define by  $\boldsymbol{S} = \boldsymbol{S}^T$  with  $\boldsymbol{C} = \boldsymbol{B}^T$  and  $\boldsymbol{D} = \boldsymbol{D}^T$ , which simplifies Equation (2.20) to

$$\hat{\boldsymbol{H}} = \begin{bmatrix} \boldsymbol{E} & \boldsymbol{F} \\ -\boldsymbol{F} & -\boldsymbol{E} \end{bmatrix}$$

(2.21)

where  $\boldsymbol{E} = \boldsymbol{A} - \boldsymbol{B} \left( \boldsymbol{D}^2 - \boldsymbol{I} \right)^{-1} \boldsymbol{D}^T \boldsymbol{C}$  and  $\boldsymbol{F} = -\boldsymbol{B} \left( \boldsymbol{D}^2 - \boldsymbol{I} \right)^{-1} \boldsymbol{C}$ . After denoting each pair of eigenvalue as  $\lambda$  and eigenvector as  $\tilde{\boldsymbol{x}}$  for  $\hat{\boldsymbol{H}}$ , one could obtain

$$[(\boldsymbol{E} + \boldsymbol{F})(\boldsymbol{E} - \boldsymbol{F}) - \lambda^2 \boldsymbol{I}] \,\tilde{\boldsymbol{x}} = 0, \qquad (2.22)$$

of which the  $\lambda$  is exactly the square-roots of the eigenvalues of the matrix

$$\boldsymbol{P} = (\boldsymbol{E} + \boldsymbol{F})(\boldsymbol{E} - \boldsymbol{F}) \tag{2.23}$$

or

$$\boldsymbol{P} = \left(\boldsymbol{A} - \boldsymbol{B}(\boldsymbol{D} - \boldsymbol{I})^{-1}\boldsymbol{C}\right) \left(\boldsymbol{A} - \boldsymbol{B}(\boldsymbol{D} + \boldsymbol{I})^{-1}\boldsymbol{C}\right).$$

(2.24)

Note that test matrix  $\boldsymbol{P}$  is only half-sized compared to the original singularity matrix  $\boldsymbol{H}$ . This change accelerates the passivity assessment roughly eight times faster, which better suits the large cases like fitting for wide frequency band. Within the band where passivity violation occurs, the eigenvalues are tuned by bringing up the minimas to the zero line. After a few checking iterations, the VF model is assured to be globally passive.

## 2.5 Construction of FNN Framework

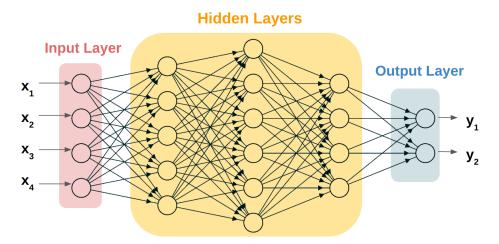

FNN is an artificial NN wherein the connections between the nodes mimics the design of human brain neurons by processing information unidirectionally along the layers. A typical architecture of FNN is shown in Figure 2.3, defining the mapping between the input features' vector  $\boldsymbol{x}$  and the output labels' vector  $\boldsymbol{y}$  through an approximation function  $\boldsymbol{y} \approx f^*(\boldsymbol{x})$ . In this particular case of FNN having three hidden layers,  $f^*$  can be decomposed to

$$f^*(\boldsymbol{x}) = f^{(3)}(f^{(2)}(f^{(1)}(\boldsymbol{x}))), \qquad (2.25)$$

where  $f^{(L)}$  denotes the *L*th hidden layer of the network. While the optimized value of *L* remains debatable [32, 33, 34, 35], a general rule of thumb is to gradually increase it until a satisfactory accuracy is achieved.

Figure 2.3: An example of FNN structure consisting of one input layer, three hidden layers and one output layer.

For a linear network, the hidden layer is oftentimes described by

$$f^{(L)}(\boldsymbol{x};\boldsymbol{\theta}) = f^{(L)}(\boldsymbol{x};\boldsymbol{W},b) = \boldsymbol{x}^{\top}\boldsymbol{W} + b, \qquad (2.26)$$

with  $\boldsymbol{W}$  being the mapping weight vector and b is the scalar bias. The exact values of  $\boldsymbol{\theta}$  are determined by locating global minimum of a cost function  $\mathcal{L}(\boldsymbol{y}, \hat{\boldsymbol{y}})$  through steepest gradient-based (SGD) optimization. A popular choice of  $\mathcal{L}$  is the mean square error (MSE) function

$$\mathcal{L}(\boldsymbol{y}, \hat{\boldsymbol{y}}) = \mathcal{L}(\boldsymbol{y}, f^*(\boldsymbol{x}; \boldsymbol{\theta})) = \left\{ \frac{1}{|\mathbb{X}|} \sum_{\boldsymbol{x} \in \mathbb{X}} (\boldsymbol{y} - f^*(\boldsymbol{x}; \boldsymbol{\theta}))^2 \right\}, \quad (2.27)$$

where the Euclidean norm between the true value  $\boldsymbol{y}$  and its approximation  $\hat{\boldsymbol{y}}$  measures how well the model explains the observed data. The optimizer seeks to solve the problem

$$\operatorname{argmin}_{\boldsymbol{\theta}} \mathcal{L}(\boldsymbol{y}, \hat{\boldsymbol{y}}) \tag{2.28}$$

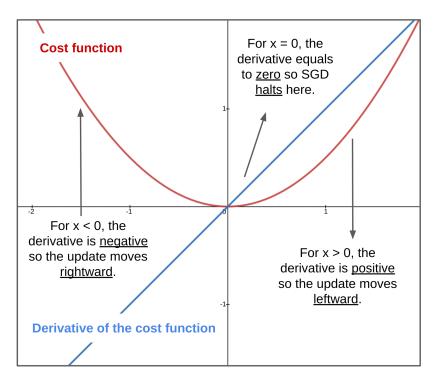

such that first derivative of the cost function  $\frac{d\mathcal{L}}{dx}$  approaches or lands on zero. This technique is essentially an iterative process because  $\theta$  is updated each time in small steps with opposite sign of the derivative. Figure 2.4 demonstrates a simple example of SGD with  $\mathcal{L} = \frac{1}{2}x^2$ . In the case where multiple inputs are presented (e.g.  $\boldsymbol{x}$  is a vector), the gradient is taken with respect to a directional vector that contains all the partial derivatives. The SGD algorithm moves in the direction of the negative gradient vector and halts when every element in the vector is equal or very close to zero.

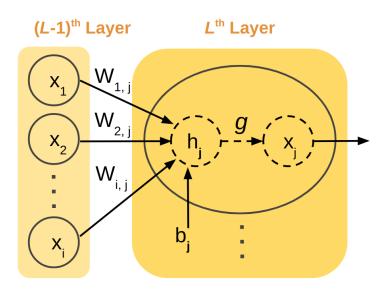

For a non-linear network, a scalar-to-scalar activation function g is introduced to compensate for the nonlinearity in the hidden layer model. As illustrated in Figure 2.5, g is applied element-wise on every node in the *L*th layer as

$$\begin{cases} h_j = \boldsymbol{x}^\top \boldsymbol{W}_{:,j} + b_j, \quad j \in [1..k] \\ f^{(L)}(\boldsymbol{x}; \boldsymbol{\theta}) = g(\boldsymbol{h}), \quad \boldsymbol{x} \in \mathbb{X} \end{cases},$$

(2.29)

where k is the total number of the nodes in the Lth layer. Depending on the application, implementations for g may be vary. Some popular choices are listed below including the hyperbolic tangent in Equation (2.30), the sigmoid function in Equation (2.31) and the rectified linear unit (ReLU) [36] in Equation (2.32).

$$g(\boldsymbol{h}) = \frac{e^{\boldsymbol{h}} - e^{-\boldsymbol{h}}}{e^{\boldsymbol{h}} + e^{-\boldsymbol{h}}}$$

(2.30)

$$g(h) = \frac{1}{1 + e^{-h}}$$

(2.31)

$$g(\boldsymbol{h}) = max\{0, \boldsymbol{h}\} \tag{2.32}$$

Figure 2.4: An illustration of how SGD searches the minimum in the cost function  $\mathcal{L} = \frac{1}{2}x^2$  using the derivatives.

Figure 2.5: Application of activation function g in the hidden layers.

The solving process for  $\boldsymbol{\theta}$  is not much different from the one for the linear system, expect the optimizer is now facing a non-convex problem. Specifically, SGD is more likely to hit a saddle point where the derivative of  $\mathcal{L}$ equals to zero and thus loss the information about which direction to move. Such a point can either be a local maximum or minimum, which blocks the SGD to arrive at the desired global minimum (see Figure 2.6). Since global convergence is no longer guaranteed, the optimization now becomes very sensitive to the initial values of the unknown parameters. Hence, it is critical to initialize W to small random values and b to zero or small positive values before the samples are sent for training [37]. Another hyper-parameter that might help escaping the suboptimal solution is the learning rate  $\eta$ , which defines the size of the updating step. The general idea is to have  $\eta$  as an adaptive variable that is large when steeping down the gradient hill and small when it is close to a potential minimum. Modern SGD like Adam [38] from Pytorch has a built-in decaying algorithm for  $\eta$ , which maintains a fair balance between training time and model accuracy.

Figure 2.6: Non-convex condition with multiple local minima.

Even with Adam, there are times, however, that the solutions are still highly unreliable due to the complex hypothesis fitting. One example is *overfitting* as illustrated in Figure 2.7, where model B is clearly a better match for the true function but has a higher MSE compared to model A. Nevertheless, from the SGD perspective, it will always prefer model B because its fitting error is zero. To prevent overfitting in the FNN model, it is a common practice to divide the collected data into training, validation and testing sets with a ratio of 70% - 10% - 20%. The sets have to be randomly selected and shuffled to ensure unbiased evaluation. In an ideal scenario, the data within each sets should be evenly distributed with some points dedicated for corner cases. During the training phase, cost function is evaluate for both the training and the validation sets as training loss and validation loss. While the training loss is used by SGD to update  $\boldsymbol{\theta}$  at each epoch, the validation loss is only calculated at the end of epoch to provide insights on the overfitting condition. Upon completion of all the epochs, one could inspect the loss plots as shown in Figure 2.8 to determine if the model overfits the function. If the model demonstrates good convergence, the reserved testing sets can be used to further verify its correctness; If overfitting occurs, one must halt the process here and deliberately calibrate how the data sets are distributed. In the end, successfully FNN training relays heavily on the given data: Sampled points in highly nonlinear and linear regions should be assigned evenly to the training, validation and testing sets.

Figure 2.7: Model A overfits the true function with low MSE.

Figure 2.8: Use validation data to prevent overfitting condition.

Figure 2.9: FNN modeling workflow for the HSL transceivers.

Figure 2.10: FNN structure for training TX with VF protocol.

## 2.6 Summary

In Figure 2.9, the FNN modeling workflow for the HSL transceivers is concluded using the protocol parameters indicated in the previous sections. First, the ground truth data is obtained from SPICE transient simulation in ADS and then transferred to python to construct memory matrices. An automation script is developed to facilitate this step as described in Appendix A. Then, based on the type of the buffer (TX/RX), different protocols are appended to the memory sequences. At the end, the matrices are fed to FNN for training as illustrated in Figure 2.10. The realization of VF and FNN training are done through python packages skrf and pytorch, respectively. More details on the python programming environment can be found in Appendix B.

## CHAPTER 3

## APPLICATION OF FNN MODELS IN HIGH SPEED LINK (HSL) SIMULATION

## 3.1 Introduction

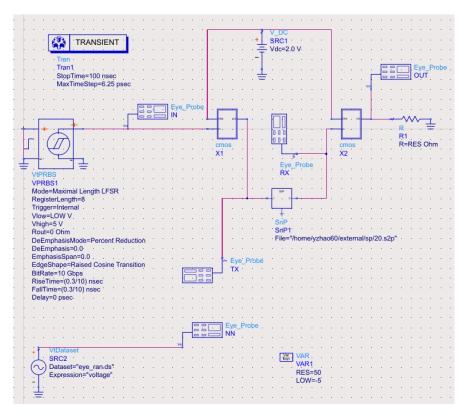

In this chapter, two transistor level gates, CMOS in Figure 3.1 and NAND in Figure 3.2, are designed in Keysight ADS and then modeled with FNN. The CMOS inverter was constructed by a PMOS and a NMOS of width/length (W/L) ratio equals to 2.5. The NAND gate was built with the same structure, except the W/L was kept at a ratio of 1 for maximum power delivery. Both gates are built upon the BSIM4 MOSFET models [39] and biased with a constant DC voltage source of 2 V. The ground truth data is obtained by running transient simulation for a 100 ns period with 10 ps time step. To ensure fairness in evaluation, only the first 50 ns of the waveform is used for training and validation while the rest is reserved for testing. The FNN employed in the following sections has three hidden layers, which all use ReLU as activation function due to its sparsity and a reduced likelihood of vanishing gradient. Adam and MSE are chosen as the optimizer and cost function, respectively. After training, the FNN models were tested with various HSL configurations, including the ones that are not available in the training setting. The correlation between the reference waveform and the FNN outputs is quantified by the coefficient of determination,  $R^2$  score, defined as

$$R^{2} = 1 - \frac{\sum_{i=1}^{N} \left\| y^{(i)} - \hat{y}^{(i)} \right\|^{2}}{\sum_{i=1}^{N} \left\| \hat{y}^{(i)} - \bar{y} \right\|^{2}}$$

(3.1)

where  $\bar{y} = (1/N) \sum_{i=1}^{N} \hat{y}^{(i)}$ . A  $R^2$  score closer to 1.0 implies a strong correlation, meaning the model is producing valid predictions for the test dataset. This metric is essentially a standardizes version of MSE with respect to the variance presented in the reference dataset as  $R^2 = 1 - (MSE/\hat{y})$ .

Figure 3.1: Transistor level circuit of CMOS inverter.

Figure 3.2: Transistor level circuit of NAND gate.

### 3.2 Trainig Environment

#### 3.2.1 TX

The FNN TX models are generated using the schematic in Figure 3.3 for CMOSs and in Figure 3.4 for NAND. The labeled inputs  $V_{IN}$ ,  $V_A$  and  $V_B$  are pseudo-random bit sequence (PRBS) and the labeled nets  $V_{TX}$  and  $V_{RX}$  are the expected outputs of the TX models. For demonstration purpose, each gate is trained with two protocols: Geometric and S-parameter (VF).

Figure 3.3: HSL configuration of cascading two CMOSs, channel and termination.

Figure 3.4: HSL configuration of cascading NAND, channel and CMOS.

In the geometric approach, the channel is a microstrip line of width w and length l. To ensure the robustness of the models, w, l and settings of PRBS are linearly swept with values shown in Table 3.1, where  $V_h/V_l$  denotes the highest/lowest voltage of PRBS dynamic range and  $B_r$  is the PRBS data rate. After collecting the voltage readings at the desired nets from ADS batch simulation, the data is sent to FNN for training. With a memory length of M = 300, the number of columns in the input matrix  $\mathbf{X}$  for CMOS and NAND are 302 and 602, respectively. The extra columns in the NAND are the result of dual-input. For a multi-inputs gate, memory sequence of each excitation is concatenated horizontally to ensure all information is recorded by the FNN. The number of neurons in each layer of FNN is designed to strictly follow the width of  $\mathbf{X}$ . For example, under the geometric protocol, the neurons adopted in the CMOS model are (M + 2),  $\frac{M+2}{2}$ , 50, 25 and 2 from input layer to output layer accordingly.

| Parameter | w (mm)    | l (mm)  | $V_h$ (V) | $V_l$ (V)   | $B_r$ (Gbps) |

|-----------|-----------|---------|-----------|-------------|--------------|

| Value     | [0.25, 6] | [0, 45] | [1, 5]    | $-V_h \& 0$ | [1, 10]      |

| Step      | 0.25      | 15      | 1         | N.A.        | 1            |

Table 3.1: Range of sweeping values in ADS batch simulation

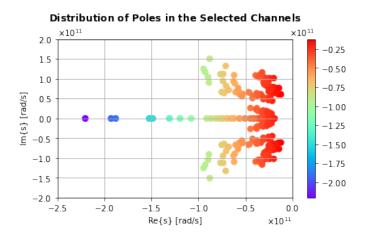

In the VF approach, the channel is characterized by S-parameters extracted from both microstrip lines and discontinued transmission lines. The geometry of the channel is varied so that the selected S-parameter samples can cover a wide range of poles as shown in Figure 3.5. During the VF, the max number of poles are set to be 4 and the fitted results are padded with zero if fewer poles are used. Since the sequential order of poles is critical for FNN but not for VF, the poles coming from VF are re-organized to have a descending order, followed by their corresponding residues. To speed up the training, it is generally recommended to have the input features normalized to a set with a mean close to zero. Given that the flattened poles, residues and constants [a, r, d] are usually multiple orders of magnitude off from this standard, normalization with  $log_{10}$  is performed before appending the set to the memory sequences. Furthermore, one might notice the channel-absent case is not available in the pre-sampled poles. This is because VF cannot fit this special case under the constrain of passivity enforcement. To add it into the training set, an extra flagging feature is applied: A padding of zeros and a flag of zero represents the without channel case; [a, r, d] followed by a flag of one resembles the with channel case.

Figure 3.5: Poles used for FNN TX training with VF.

#### 3.2.2 RX

The FNN CMOS RX model is generated using the schematic in Figure 3.3 by taking voltages of  $V_{RX}$  and  $V_{OUT}$  as references. The channels designed for VF protocols are re-used here to ensure that the RX model is capable of interpreting noisy  $V_{RX}$ . During the ADS batch simulation, the PRBS settings are varied in the same manner as above and the resistive termination  $r_t = [5, 100000] \Omega$  is swept logarithmically at a step of 3  $\Omega$ /decade. Since the RX model only oversees a resistor, M is chosen to be 50, which greatly reduces the size of layers in FNN. Normalization with  $log_{10}$  is applied on the termination feature before concatenating it to the memory matrix.

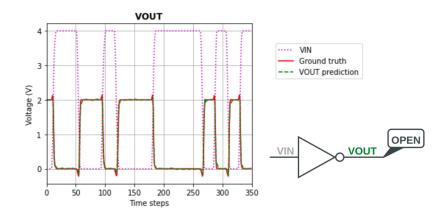

## 3.3 HSL Configuration with NRZ Excitation

Before showing the cascade-ability of the FNN models, the accuracy of a single building block is verified. Figure 3.6 illustrates the test case of a standalone CMOS connected to an open termination with a PRBS excitation of  $V_l = 0$  V,  $V_h = 4$  V and  $B_r = 5$  Gbps. In this case, the CMOS RX model is employed with the termination condition set to near open ( $r_t = 100000 \ \Omega$ ). The  $V_{OUT}$  prediction has a  $R^2$  score of 0.989, which confirms the validity of the FNN model.

Figure 3.6: FNN prediction for a stand-alone CMOS with open termination.

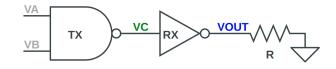

Next, a comparison is drawn between the two TX protocols. For the HSL configuration shown in Figure 3.7, either of the FNN NAND TX models could be used to predict the voltage waveform at node  $V_C$ :

- Geometric: Set l = 0 mm and 0.25 mm  $\leq w \leq 6$  mm.

- VF: Set the padding and the flag features to zeros.

Since this example is a special case of directly cascading TX with RX, the two outputs yield by the TX models essentially describe the same node:  $V_{TX} = V_{RX} = V_C$ . Given a PRBS excitation of  $V_l = 0$  V,  $V_h = 3$  V,  $B_{r(A)} = 3$  Gbps and  $B_{r(B)} = 4$  Gbps, the modeling results from the two protocols are plotted and compared as shown in Figure 3.8. Although tiny variations exist between the two models, both protocol yield prediction of  $R^2 = 0.998$  in respect to the reference voltage. Hence we can safely assume that either of the predicted  $V_C$  is valid as input to the CMOS RX model. After feeding  $V_C$  from the VF TX model to the RX model, a cascading chain of FNN models is established where good agreement is found between the predicted and true value of  $V_{OUT}$  (see Figure 3.9). In this case, the  $R^2$  score is 0.996.

Figure 3.7: HSL configuration of cascading NAND, CMOS and termination.

Figure 3.8: Comparison of NAND TX model predictions on  $V_C$ .

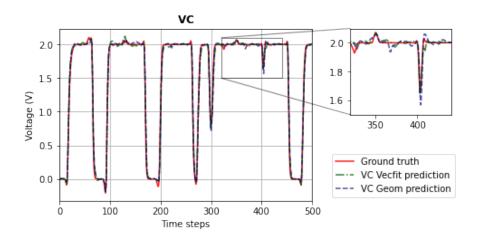

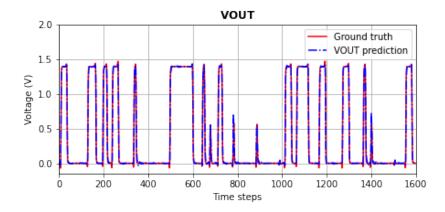

Moreover, a test configuration consisting of multiple CMOS gates is evaluated to further demonstrate the cascade-ability of the FNN models. As shown in Figure 3.10, a PRBS sequence of  $V_l = 0$  V,  $V_h = 5$  V and  $B_r = 1$

Figure 3.9: FNN prediction of  $V_{OUT}$  in Figure 3.7 with termination  $r_t = 50 \ \Omega$ .

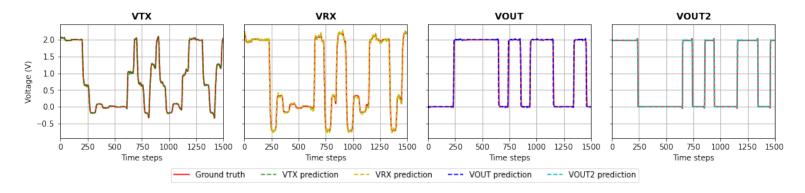

Gbps is fed through a HSL followed by an extra CMOS and a 2000  $\Omega$  termination. The channel within the HSL is a microstrip line of w = 6 mm and l = 45 mm. First, the CMOS TX model with geometric protocol is used to make predictions on  $V_{TX}$  and  $V_{RX}$ . Then, the predicted  $V_{RX}$  is delivered to the CMOS RX model for  $V_{OUT}$  prediction. Although there is no termination directly connected with  $V_{OUT}$ , RX sees the extra CMOS almost as an open load. Due to this, the termination feature is set to max so the prediction matches with its reference. At the end,  $V_{OUT2}$  is obtained by forwarding the predict  $V_{OUT}$  through the RX model with  $r_t = 2000 \ \Omega$ . Predicted waveforms at each node are presented in Figure 3.11. The  $R^2$  scores for  $V_{TX}$ ,  $V_{RX}$ ,  $V_{OUT}$  and  $V_{OUT2}$  are 0.999, 0.998, 0.989 and 0.986, respectively.

Figure 3.10: A cascading chain of multiple CMOSs, channel and termination.

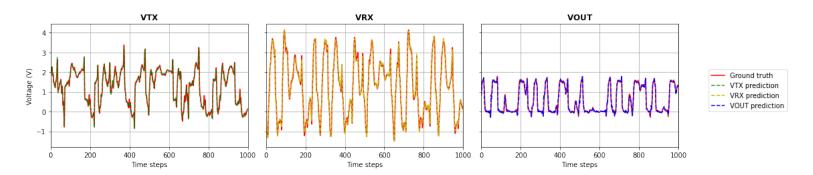

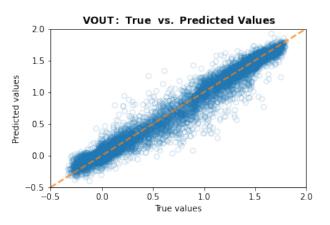

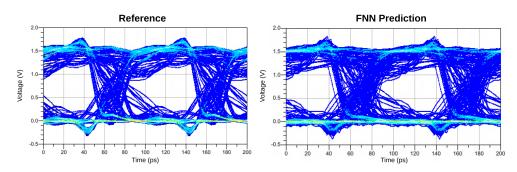

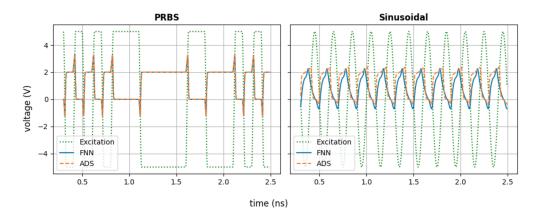

Lastly, the FNN CMOS models are cascaded to reproduce the eye digram at node  $V_{OUT}$  in the HSL schematic shown in Figure 3.3. Given a PRBS excitation of  $V_l = -5$  V,  $V_h = 5$  V and  $B_r = 10$  Gbps along with a Sparameter characterized channel, the voltage waveforms predicted by the FNN models are shown in Figure 3.12. Fairly good correlation is achieved with a  $R^2$  score of 0.983, 0.986 and 0.982 for  $V_{TX}$ ,  $V_{RX}$  and  $V_{OUT}$ .

Figure 3.11: FNN predictions of  $V_{TX}$ ,  $V_{RX}$ ,  $V_{OUT}$ ,  $V_{OUT2}$  in a three CMOSs cascading chain.